新的数字合成实验室继承了David Harris和Sarah Harris的教程“数字电路与计算机体系结构”的传统,该教程下载了英国站点。通过本实验,您可以在FPGA板上触及Harris和Harris的全部理论,从闪光灯到处理器。还在实验室中分析了传送带处理的概念,没有传送带处理,您将不会通过面试以在任何微电子公司中担任设计师。最后,是从FPGA到ASIC的路径,iPhone,Tesla和AI加速器中的大规模电路。这本书包含对圣彼得堡团队的采访,英特尔将他们带到了位于硅谷的总部,以表彰他们在创新FPGA竞赛中的胜利。图书“数字综合:实践课程”支持微电路设计自动化的领先公司Cadence Design Systems(在上图中,Siberian Natasha站在FPGA板在Cadence硅谷总部的前面,她的视频将在帖子中)。Labnik是在主持下建立高等经济学院/ MIEM的(亚历山大·罗曼诺夫,纯美Prokhorova和伊戈尔Agamirzyan),而不同的章节是由来自莫斯科,基辅和萨马拉大学,圣彼得堡ITMO,切尔尼戈夫理工学院和加州大学圣克鲁兹(大学教师写查尔斯Danchek,硅谷的晚上办公室)。俄罗斯IVA Technologies公司的工程师(Stanislav Zhelnio,硬件加速器AI + 教育项目学校MIPS)参加了教科书的创建)和FSUE NPTSAP(罗斯科斯莫斯分公司),美国公司MIPS,Juniper Networks和AMD。出版了教科书DMK-Press。我为实验室制定了一个计划,并从以前的教育项目中吸引了作者,此后,我将控制权移交给了亚历山大·罗曼诺夫,后者进行了艰苦的工作,管理了该项目近两年。教科书的创建自然适合Alexander的活动,Alex三年来在HSE MIEM成立了实验室,该实验室处理嵌入式计算机,机器人和FPGA。该实验室在Innovate FPGA中组织了多个团队,其中一个团队在地区决赛中获得铜牌。该教科书不仅适合学生,还可以用于高级学生的数字设计夏令营。从零开始了解Internet上有关如何使用Intel Quartus II环境的教程并非易事。并且在教科书中全部分步描述。此外,除了闪光灯会很快困扰他们外,它还为学童做一些有趣的事情提供了所有理论依据。例如,有趣的是一个视频游戏:

新的数字合成实验室继承了David Harris和Sarah Harris的教程“数字电路与计算机体系结构”的传统,该教程下载了英国站点。通过本实验,您可以在FPGA板上触及Harris和Harris的全部理论,从闪光灯到处理器。还在实验室中分析了传送带处理的概念,没有传送带处理,您将不会通过面试以在任何微电子公司中担任设计师。最后,是从FPGA到ASIC的路径,iPhone,Tesla和AI加速器中的大规模电路。这本书包含对圣彼得堡团队的采访,英特尔将他们带到了位于硅谷的总部,以表彰他们在创新FPGA竞赛中的胜利。图书“数字综合:实践课程”支持微电路设计自动化的领先公司Cadence Design Systems(在上图中,Siberian Natasha站在FPGA板在Cadence硅谷总部的前面,她的视频将在帖子中)。Labnik是在主持下建立高等经济学院/ MIEM的(亚历山大·罗曼诺夫,纯美Prokhorova和伊戈尔Agamirzyan),而不同的章节是由来自莫斯科,基辅和萨马拉大学,圣彼得堡ITMO,切尔尼戈夫理工学院和加州大学圣克鲁兹(大学教师写查尔斯Danchek,硅谷的晚上办公室)。俄罗斯IVA Technologies公司的工程师(Stanislav Zhelnio,硬件加速器AI + 教育项目学校MIPS)参加了教科书的创建)和FSUE NPTSAP(罗斯科斯莫斯分公司),美国公司MIPS,Juniper Networks和AMD。出版了教科书DMK-Press。我为实验室制定了一个计划,并从以前的教育项目中吸引了作者,此后,我将控制权移交给了亚历山大·罗曼诺夫,后者进行了艰苦的工作,管理了该项目近两年。教科书的创建自然适合Alexander的活动,Alex三年来在HSE MIEM成立了实验室,该实验室处理嵌入式计算机,机器人和FPGA。该实验室在Innovate FPGA中组织了多个团队,其中一个团队在地区决赛中获得铜牌。该教科书不仅适合学生,还可以用于高级学生的数字设计夏令营。从零开始了解Internet上有关如何使用Intel Quartus II环境的教程并非易事。并且在教科书中全部分步描述。此外,除了闪光灯会很快困扰他们外,它还为学童做一些有趣的事情提供了所有理论依据。例如,有趣的是一个视频游戏: 通过VGA游戏学习Verilo的想法并不新鲜-许多大学都有这样的实验室,例如在麻省理工学院(MIT)6.111入门数字系统实验室。同样,两年前,史蒂文·哈格(Steven Hugg)出版了《在Verilog平装本上设计视频游戏硬件》一书,其中包括坦克,赛车,使用LFSR的伪随机星空生成器,帧缓冲器甚至硬件-软件接口的相当发达的游戏。此外,FPGA Xilinx和Intel / Altera的制造商(更确切地说是其合作伙伴Digilent和Terasic)的演示中都包含VGA游戏。

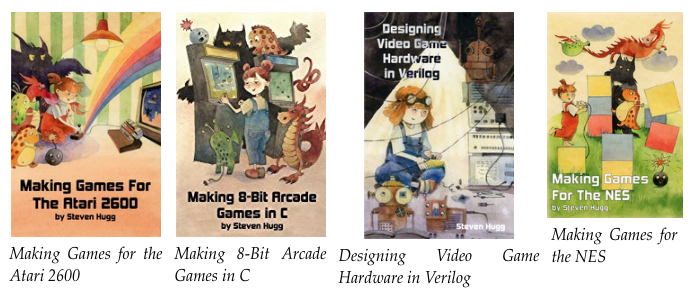

通过VGA游戏学习Verilo的想法并不新鲜-许多大学都有这样的实验室,例如在麻省理工学院(MIT)6.111入门数字系统实验室。同样,两年前,史蒂文·哈格(Steven Hugg)出版了《在Verilog平装本上设计视频游戏硬件》一书,其中包括坦克,赛车,使用LFSR的伪随机星空生成器,帧缓冲器甚至硬件-软件接口的相当发达的游戏。此外,FPGA Xilinx和Intel / Altera的制造商(更确切地说是其合作伙伴Digilent和Terasic)的演示中都包含VGA游戏。 特别是在麻省理工学院的实验室中很清楚地表明,您需要在显示器上绘制的所有内容就是以图的形式实现一个函数,该函数以屏幕上某个点的坐标X和Y作为参数,并返回该点的颜色(RGB)。在最简单的情况下,此函数是组合函数,例如,此函数将绘制Malevich的杰作:“如果x> = 200且x <= 400且y> = 200且y <400,则颜色为黑色(RGB = 0,0,0),否则为白色(RGB = 1,1,1)。”我们将这种电路进一步称为“混合器”,因为它将“混合”来自不同图像生成器的输入。为了自己生成混频器参数X和Y,使用了一个简单的两计数器电路,该电路使用CLK时钟信号。除了X和Y坐标外,该电路还为VGA显示生成HSYNC和VSYNC信号。自阴极射线管以来,HSYNC和VSYNC信号一直保留。他们告诉虚拟光束何时水平移动到屏幕上的下一个点/像素,然后垂直移动到下一行。在困难的情况下,混频器不仅使用其输入X和Y的值,而且还使用状态元素(D触发器和存储器)中的值,这些值是使用CLK时钟信号记录的。在这种情况下,时钟也进入混频器。具有时钟信号和状态元素的电路称为顺序电路(这些电路经过一系列状态,这些状态清楚地使脉动的时钟信号产生脉动)。在顺序混合器上,您可以实现任何复杂程度的运动图像。这是MIT shnaya实验室的图片(与其他大学的图片相同),它们说明了HSYNC / VSYNC生成器的功能,混频器(同一单元的功能,该单元根据X / HCOUNT和Y / VCOUNT计算RGB)以及HSYNC的输出,屏幕上的VSYNC和RGB。该图片在三个混音器之间使用了一个开关/多路复用器-一个画条纹,另一个画一个矩形,而第三个则在打乒乓球时

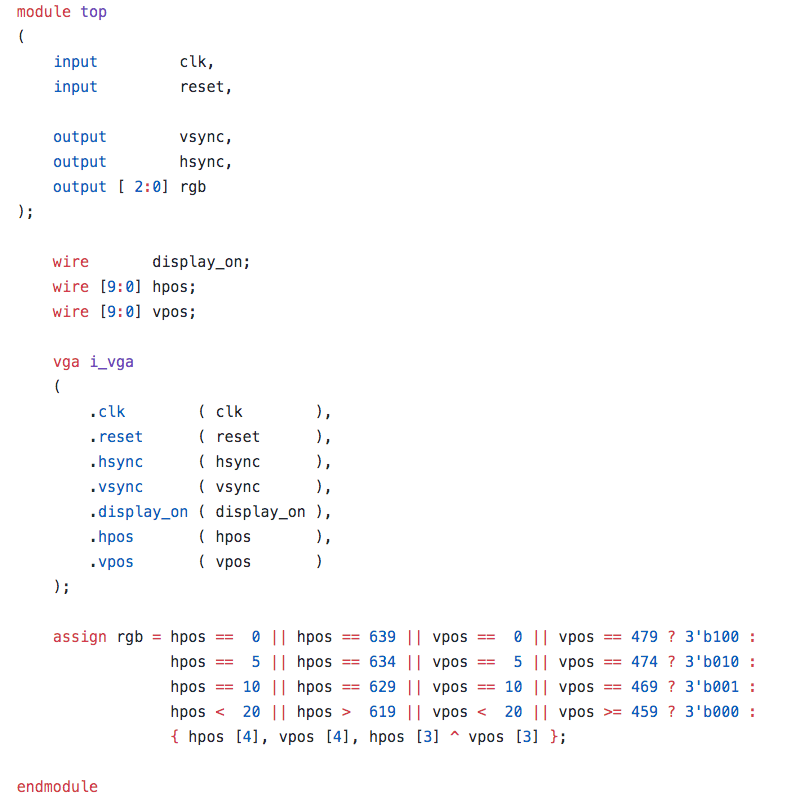

特别是在麻省理工学院的实验室中很清楚地表明,您需要在显示器上绘制的所有内容就是以图的形式实现一个函数,该函数以屏幕上某个点的坐标X和Y作为参数,并返回该点的颜色(RGB)。在最简单的情况下,此函数是组合函数,例如,此函数将绘制Malevich的杰作:“如果x> = 200且x <= 400且y> = 200且y <400,则颜色为黑色(RGB = 0,0,0),否则为白色(RGB = 1,1,1)。”我们将这种电路进一步称为“混合器”,因为它将“混合”来自不同图像生成器的输入。为了自己生成混频器参数X和Y,使用了一个简单的两计数器电路,该电路使用CLK时钟信号。除了X和Y坐标外,该电路还为VGA显示生成HSYNC和VSYNC信号。自阴极射线管以来,HSYNC和VSYNC信号一直保留。他们告诉虚拟光束何时水平移动到屏幕上的下一个点/像素,然后垂直移动到下一行。在困难的情况下,混频器不仅使用其输入X和Y的值,而且还使用状态元素(D触发器和存储器)中的值,这些值是使用CLK时钟信号记录的。在这种情况下,时钟也进入混频器。具有时钟信号和状态元素的电路称为顺序电路(这些电路经过一系列状态,这些状态清楚地使脉动的时钟信号产生脉动)。在顺序混合器上,您可以实现任何复杂程度的运动图像。这是MIT shnaya实验室的图片(与其他大学的图片相同),它们说明了HSYNC / VSYNC生成器的功能,混频器(同一单元的功能,该单元根据X / HCOUNT和Y / VCOUNT计算RGB)以及HSYNC的输出,屏幕上的VSYNC和RGB。该图片在三个混音器之间使用了一个开关/多路复用器-一个画条纹,另一个画一个矩形,而第三个则在打乒乓球时 在屏幕上画一个图像:在代码中,最简单的混合器如下所示。他用红色,蓝色和绿色的混合物以及纯色线条绘制了彩色正方形:

在屏幕上画一个图像:在代码中,最简单的混合器如下所示。他用红色,蓝色和绿色的混合物以及纯色线条绘制了彩色正方形: 这样,您就可以绘制各种彩色的静态图像。这是学生在简短讲解后立即在Zelenograd的一所暑期学校绘制的图像:

这样,您就可以绘制各种彩色的静态图像。这是学生在简短讲解后立即在Zelenograd的一所暑期学校绘制的图像: 好吧,小学生可以对RGB(X,Y)函数进行编码并绘制静态图片。但是下一步该怎么做,下一步是什么?我们研究了使用麻省理工学院,Digilent + Xilinx,Altera + Terasic和Steven Hugg的材料的可能性,然后得出结论,它们不能以其纯净形式使用。大学计划中包括大学实验室,而来自FPGA供应商的材料写得不好,也没有包含有关如何以暑期学校的格式更改代码以使学生发明游戏的技巧。史蒂芬·哈格(Stephen Hugg)的书有两个缺点,即其美德的另一面(生动和丰富多彩):通常,Stephen Hugg的Verilog与Atari和Nintendo的旧8位控制台的处理器编程保持一致。因此,Hugg的重点不是培训未来的超级设计师,而是怀旧的人,复古的计算机科学家和其他角色。他的环境与专业设计工具之间的差异甚至比Arduino编程环境与STM32工具包之间的差异还要大。

好吧,小学生可以对RGB(X,Y)函数进行编码并绘制静态图片。但是下一步该怎么做,下一步是什么?我们研究了使用麻省理工学院,Digilent + Xilinx,Altera + Terasic和Steven Hugg的材料的可能性,然后得出结论,它们不能以其纯净形式使用。大学计划中包括大学实验室,而来自FPGA供应商的材料写得不好,也没有包含有关如何以暑期学校的格式更改代码以使学生发明游戏的技巧。史蒂芬·哈格(Stephen Hugg)的书有两个缺点,即其美德的另一面(生动和丰富多彩):通常,Stephen Hugg的Verilog与Atari和Nintendo的旧8位控制台的处理器编程保持一致。因此,Hugg的重点不是培训未来的超级设计师,而是怀旧的人,复古的计算机科学家和其他角色。他的环境与专业设计工具之间的差异甚至比Arduino编程环境与STM32工具包之间的差异还要大。 当然,我不建议将学童的Cadence SimVision和Synopsys Design编译器归咎于数十万美元,但学童可能会免费获取专业工具的免费版本Xilinx Vivado,Intel / Altera Quartus II,Mentor ModelSim,Icarus Verilog,GTKWave和在线edaplayground。 com。我重读了上一段,并认为:但是可以使用Zelenograd暑期学校的Cadence SimVision。它的直接竞争对手Synopsys Design Vision Environment(DVE)*,以及Mentor Graphics的资金(免费的ModelSim和Questa付费产品),以及所有便宜的免费工具(IcarusVerilog等),都变得更好,更方便。如果Cadence的莫斯科分支机构设计系统将为我们提供在Zelenograd暑期学校中使用其软件的权利和支持,我个人将其整合到学校课程中。*例如,对于DVE,当我在Ubuntu下运行时,源代码窗口中的文本有错误/跳跃。我必须调整窗口大小,直到它停止失败为止。SimVision没有此功能。这是SimVision教程的开始(总共22个视频):但是回到游戏。如果不是斯蒂芬·哈格,那又如何?我写了一个简单的游戏示例,该游戏是我在Zelenograd一家暑期学校使用的游戏。游戏的源代码在github上。看起来像这样:在两周的时间里,学生们在注册转让的层面上弄清了设计的基本原理,并开始制作自己的非平凡游戏:让我们谈谈示例游戏的技术细节。与平台无关的游戏模块可以放置(实例化)在具有VGA端口和两个按钮的任何FPGA板的包装中。如果板子完全裸露,则可以通过GPIO(通用输入/输出)线将VGA适配器和按钮连接到板上。游戏模块包括:

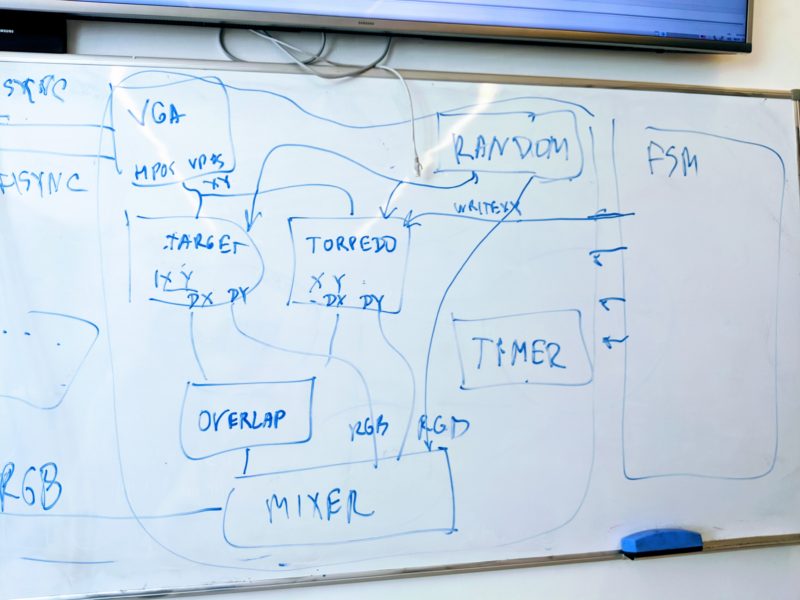

当然,我不建议将学童的Cadence SimVision和Synopsys Design编译器归咎于数十万美元,但学童可能会免费获取专业工具的免费版本Xilinx Vivado,Intel / Altera Quartus II,Mentor ModelSim,Icarus Verilog,GTKWave和在线edaplayground。 com。我重读了上一段,并认为:但是可以使用Zelenograd暑期学校的Cadence SimVision。它的直接竞争对手Synopsys Design Vision Environment(DVE)*,以及Mentor Graphics的资金(免费的ModelSim和Questa付费产品),以及所有便宜的免费工具(IcarusVerilog等),都变得更好,更方便。如果Cadence的莫斯科分支机构设计系统将为我们提供在Zelenograd暑期学校中使用其软件的权利和支持,我个人将其整合到学校课程中。*例如,对于DVE,当我在Ubuntu下运行时,源代码窗口中的文本有错误/跳跃。我必须调整窗口大小,直到它停止失败为止。SimVision没有此功能。这是SimVision教程的开始(总共22个视频):但是回到游戏。如果不是斯蒂芬·哈格,那又如何?我写了一个简单的游戏示例,该游戏是我在Zelenograd一家暑期学校使用的游戏。游戏的源代码在github上。看起来像这样:在两周的时间里,学生们在注册转让的层面上弄清了设计的基本原理,并开始制作自己的非平凡游戏:让我们谈谈示例游戏的技术细节。与平台无关的游戏模块可以放置(实例化)在具有VGA端口和两个按钮的任何FPGA板的包装中。如果板子完全裸露,则可以通过GPIO(通用输入/输出)线将VGA适配器和按钮连接到板上。游戏模块包括:- VGA扫描生成器。

- 两个并行工作模块,用于精灵鱼雷和精灵目标。

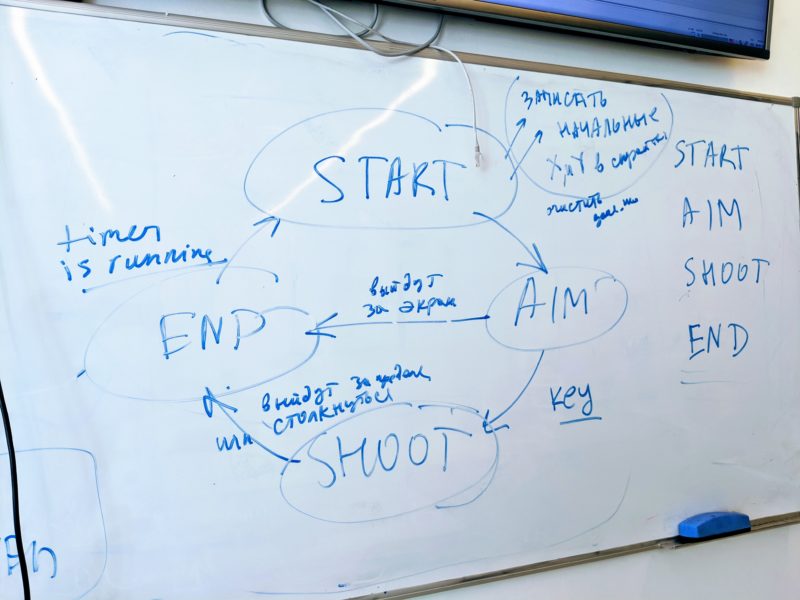

- 游戏场景的状态机,状态为“开始”,“指导”,“飞行”,“胜利/失败”。

- 确定小精灵是否发生碰撞的模块。

- 一个计时器,用于设置赢得(闪烁的树莓屏幕)或失败(黄色屏幕)后视觉效果的持续时间。

对于下一所学校,所有这些图片都需要使用draw.io或Lucidchart重绘为普通的微体系结构图:您

对于下一所学校,所有这些图片都需要使用draw.io或Lucidchart重绘为普通的微体系结构图:您 还需要将用WaveDrom绘制的时间线添加到学校资料中,以显示VGA扫描生成器如何工作以及迷你管道如何计算坐标Sprite中的数据路径:

还需要将用WaveDrom绘制的时间线添加到学校资料中,以显示VGA扫描生成器如何工作以及迷你管道如何计算坐标Sprite中的数据路径: 当然,您需要绘制有限状态机的图。我制作了该游戏的有限状态机的十二种变体,板上有四种状态的变体:

当然,您需要绘制有限状态机的图。我制作了该游戏的有限状态机的十二种变体,板上有四种状态的变体: 为什么我有很多选择?即使使用如此简单的机器,您也可以在一个面纱上比较其编码的不同样式,以及说明状态和时序的优化。所有这些都在采访中被要求在苹果,NVidia,英特尔,AMD和其他公司担任芯片设计师。因此,必须知道该区域,以便牙齿弹跳。关于此主题,有一些很好的Clifford Cummings文章:

为什么我有很多选择?即使使用如此简单的机器,您也可以在一个面纱上比较其编码的不同样式,以及说明状态和时序的优化。所有这些都在采访中被要求在苹果,NVidia,英特尔,AMD和其他公司担任芯片设计师。因此,必须知道该区域,以便牙齿弹跳。关于此主题,有一些很好的Clifford Cummings文章:- 2019年最新文章:使用SystemVerilog进行FiniteStateMachine(FSM)设计和综合-第一部分,作者Clifford E.Cummings和Heath Chambers。

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

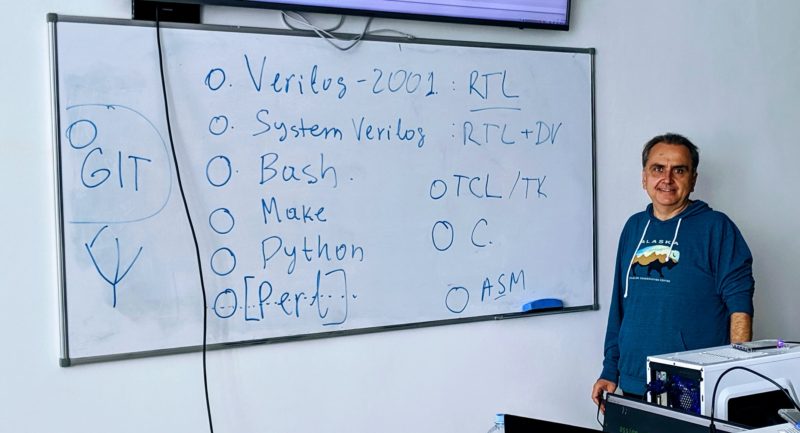

我使用业界最流行的Synopsys Design Compiler工具合成了游戏状态机的不同版本,并制成了这种平板电脑。如我们所见,现代版本的DC非常有效地优化了所有样式,因此可以在状态机上拉皮秒,但这不是必需的。尽管可能使用更复杂的有限状态机,但Cummings文章中的技巧将变得更加关键: 在Zelenograd上学期间,我们还讨论了在芯片设计中,除了Verilog和VHDL设备的描述语言之外,还使用了许多辅助语言:

在Zelenograd上学期间,我们还讨论了在芯片设计中,除了Verilog和VHDL设备的描述语言之外,还使用了许多辅助语言:Python用于自动组装,回归管理,并从综合和代码生成报告以及bash,make和其他Unix / Linux厨房中提取信息。

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++和诸如SystemC之类的库用于编写事务级硬件块模型。验证工程师会根据这些模型检查在面纱上设计的模块。

如果您在处理器公司工作,那么对汇编程序的了解对您很有帮助。即使您不是底层程序员,也不是验证者,但是您是寄存器传输级别(Register Transfer Level-RTL)的处理器设计者。

对于那些有兴趣使用珍珠作为预处理程序的人,这里是链接:- G.斯皮维。EP3:可扩展的Perl预处理器

- vpp.pl手册页

- Verilog预处理器

如何使用内置的verlog pearl连接64个端口的示例://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

如果有人编写了通用脚本来在所有主要平台上进行建模和综合示例(不一定是我的游戏),以进行综合,仿真,调试,动态功耗分析,物理设计,对所有电路板的绑定等,那将是很好的。可用于学校和研讨会:

如果有人编写了通用脚本来在所有主要平台上进行建模和综合示例(不一定是我的游戏),以进行综合,仿真,调试,动态功耗分析,物理设计,对所有电路板的绑定等,那将是很好的。可用于学校和研讨会: 在这里您可能会有一个问题:为什么要使用Linux研讨会?尽管Windows也具有用于FPGA的建模和综合环境,但Windows尚未在大规模芯片设计行业扎根。在1990年代初期,面向ASIC开发人员的工作站市场被SunOS和HP / UX所分割。然后,电子公司使用Windows NT玩了三年,但没有成功。之后,Synopsys和其他设计软件公司吐口水并改用Linux-首先是在Red Hat,然后是SuSE和Ubuntu。我怀疑,主要是由于珍珠,C-shell等上的一堆脚本以及开发人员通过telnet和X Window进行的远程工作。因此,在我的研讨会上,我会使用一堆带有Lubuntu的可启动SSD,上面装有所有必要的软件。我使用旧版引导,但最近发现越来越多的计算机需要UEFI引导。显然,您需要使用UEFI引导制作可引导的SSD。快速发展的公司使用CentOS代替Red Hat。也许许多设计工具都在Debian下进行,但是我还没有对其进行测试。

在这里您可能会有一个问题:为什么要使用Linux研讨会?尽管Windows也具有用于FPGA的建模和综合环境,但Windows尚未在大规模芯片设计行业扎根。在1990年代初期,面向ASIC开发人员的工作站市场被SunOS和HP / UX所分割。然后,电子公司使用Windows NT玩了三年,但没有成功。之后,Synopsys和其他设计软件公司吐口水并改用Linux-首先是在Red Hat,然后是SuSE和Ubuntu。我怀疑,主要是由于珍珠,C-shell等上的一堆脚本以及开发人员通过telnet和X Window进行的远程工作。因此,在我的研讨会上,我会使用一堆带有Lubuntu的可启动SSD,上面装有所有必要的软件。我使用旧版引导,但最近发现越来越多的计算机需要UEFI引导。显然,您需要使用UEFI引导制作可引导的SSD。快速发展的公司使用CentOS代替Red Hat。也许许多设计工具都在Debian下进行,但是我还没有对其进行测试。 在研讨会上,我使用中文FPGA板,其中一个由新西伯利亚女孩Natasha握在手中,娜塔莎正在我们的硅谷举办“ What-Where-When-party”。

在研讨会上,我使用中文FPGA板,其中一个由新西伯利亚女孩Natasha握在手中,娜塔莎正在我们的硅谷举办“ What-Where-When-party”。 3月,我和俄罗斯商人谢尔盖·佐林(Sergei Zorin)一起穿越了加州野生动植物,他带了十二个ZEOWAA董事会到莫斯科,其特征与Natasha所持董事会的特征相似。由于今年夏天由于冠状病毒,在泽列诺格勒可能不会举行任何研讨会,我想我将免费给莫斯科学童这十几笔费用(UPD:来自其他城市的学童也可以,尽管转发方面还有其他麻烦)。有两个条件:

3月,我和俄罗斯商人谢尔盖·佐林(Sergei Zorin)一起穿越了加州野生动植物,他带了十二个ZEOWAA董事会到莫斯科,其特征与Natasha所持董事会的特征相似。由于今年夏天由于冠状病毒,在泽列诺格勒可能不会举行任何研讨会,我想我将免费给莫斯科学童这十几笔费用(UPD:来自其他城市的学童也可以,尽管转发方面还有其他麻烦)。有两个条件:在你获得一个董事,你需要去通过网上课程“如何做的智能纳米片作品的创造者”的所有三个部分(“从晶体管到微电路”,“数字电路的逻辑侧面”,“数字电路的物理方”),并获得了证书。我们与RUSNANO或更确切地说是其教育女儿eNano(STEMford项目)一起创建了此课程。

, , , . , , , ( ) . , , .

, , .

如果您想购买一本新书《逻辑综合》作为此类项目的辅助工具,那么对于哈伯的读者来说,她有一个促销代码-Sintez_2020。 将来,最好使用中国板,并使用开放设计的FPGA通过这种练习制造便宜的俄罗斯板。我欢迎您在板设计软件的评论中分享您的想法,以及有关如何更好地设计和销售这种板的想法。对于小学生的大规模使用,希望它的成本不超过30美元或2000卢布。

将来,最好使用中国板,并使用开放设计的FPGA通过这种练习制造便宜的俄罗斯板。我欢迎您在板设计软件的评论中分享您的想法,以及有关如何更好地设计和销售这种板的想法。对于小学生的大规模使用,希望它的成本不超过30美元或2000卢布。 如果您是学生并且对微电路设计感兴趣,可以去MIET,HSE MIEM,莫斯科工程物理研究所,莫斯科国立大学,莫斯科物理与技术研究所(Nikita Polyakov从事此类练习),MPEI,MISiS,ITMO,LETI,萨马拉大学,一些乌克兰大学(KNU,切尔尼希夫NTU,Kharkov KNURE)和其他大学。因此,我发现如何修复在Zelenograd的MIET选拔委员会的方法:

如果您是学生并且对微电路设计感兴趣,可以去MIET,HSE MIEM,莫斯科工程物理研究所,莫斯科国立大学,莫斯科物理与技术研究所(Nikita Polyakov从事此类练习),MPEI,MISiS,ITMO,LETI,萨马拉大学,一些乌克兰大学(KNU,切尔尼希夫NTU,Kharkov KNURE)和其他大学。因此,我发现如何修复在Zelenograd的MIET选拔委员会的方法: 但这是MIET内部的面貌:您可以

但这是MIET内部的面貌:您可以 在MIET对面的ELVIS NGO找份工作,该部门负责处理智能相机和卫星芯片:

在MIET对面的ELVIS NGO找份工作,该部门负责处理智能相机和卫星芯片: 或者您可以来硅谷。想要接受Dolina的采访吗?在FPGA板上练习!

或者您可以来硅谷。想要接受Dolina的采访吗?在FPGA板上练习!