O novo laboratório de Síntese Digital continua a tradição do tutorial de David Harris e Sarah Harris, Digital Circuitry and Computer Architecture, que baixou o site britânico . O laboratório permite que você toque em toda a teoria da Harris & Harris na placa FPGA, desde luzes piscantes até o processador. O conceito de processamento de transportadores também é analisado em laboratório, sem o qual você não passará por uma entrevista para trabalhar como designer em qualquer empresa de microeletrônica. No final, o caminho do FPGA para o ASIC, circuitos de massa que estão nos aceleradores iPhones, Tesla e AI.O livro contém uma entrevista com uma equipe de São Petersburgo que a Intel trouxe para sua sede no Vale do Silício para sua vitória no concurso Innovate FPGA. Livro "Síntese Digital: Um Curso Prático"A Cadence Design Systems, empresa líder em automação do design de chips, é apoiada (na foto acima, a Siberian Natasha está de pé com uma placa FPGA em frente à sede da Cadence no Vale do Silício - o vídeo dela será publicado).Labnik foi criado sob os auspícios da Escola Superior de Economia / MIEM (Alexander Romanov, Veronika Prokhorova e Igor Agamirzyan), enquanto diferentes capítulos foram escritos por professores das universidades de Moscou, Kiev e Samara, ITMO de São Petersburgo, ITMO de São Petersburgo, Politécnica de Chernihiv e da Universidade da Califórnia em Santa Cruz ( Charles Danchek , noite no Vale do Silício). A criação do livro contou com a participação de engenheiros da empresa russa IVA Technologies (Stanislav Zhelnio, acelerador de hardware AI + projeto educacional schoolMIPS) e FSUE NPTSAP(departamento de Roscosmos), empresas americanas MIPS, Juniper Networks e AMD. Publicou um livro didático DMK-Press.Elaborei um plano para o laboratório e atraí autores de projetos educacionais anteriores, após o que transferi o controle para Alexander Romanov, que realizou um trabalho minucioso, gerenciando o projeto por quase dois anos. A criação do livro didático naturalmente se encaixa nas atividades de Alexander , que por 3 anos criou o laboratório no HSE MIEM , que lida com computadores embarcados, robótica e FPGAs. O laboratório organizou várias equipes no Innovate FPGA, uma das quais se tornou medalhista de bronze nas finais regionais.O livro não é apenas adequado para estudantes - pode ser usado em acampamentos de verão de design digital para estudantes avançados. Noções básicas sobre tutoriais na Internet do zero sobre como trabalhar com o ambiente Intel Quartus II não é trivial. E no livro está tudo descrito em etapas. Além disso, possui toda a base teórica para fazer algo interessante para as crianças em idade escolar, além de luzes piscantes que as incomodam rapidamente. Interessante é, por exemplo, um videogame:

O novo laboratório de Síntese Digital continua a tradição do tutorial de David Harris e Sarah Harris, Digital Circuitry and Computer Architecture, que baixou o site britânico . O laboratório permite que você toque em toda a teoria da Harris & Harris na placa FPGA, desde luzes piscantes até o processador. O conceito de processamento de transportadores também é analisado em laboratório, sem o qual você não passará por uma entrevista para trabalhar como designer em qualquer empresa de microeletrônica. No final, o caminho do FPGA para o ASIC, circuitos de massa que estão nos aceleradores iPhones, Tesla e AI.O livro contém uma entrevista com uma equipe de São Petersburgo que a Intel trouxe para sua sede no Vale do Silício para sua vitória no concurso Innovate FPGA. Livro "Síntese Digital: Um Curso Prático"A Cadence Design Systems, empresa líder em automação do design de chips, é apoiada (na foto acima, a Siberian Natasha está de pé com uma placa FPGA em frente à sede da Cadence no Vale do Silício - o vídeo dela será publicado).Labnik foi criado sob os auspícios da Escola Superior de Economia / MIEM (Alexander Romanov, Veronika Prokhorova e Igor Agamirzyan), enquanto diferentes capítulos foram escritos por professores das universidades de Moscou, Kiev e Samara, ITMO de São Petersburgo, ITMO de São Petersburgo, Politécnica de Chernihiv e da Universidade da Califórnia em Santa Cruz ( Charles Danchek , noite no Vale do Silício). A criação do livro contou com a participação de engenheiros da empresa russa IVA Technologies (Stanislav Zhelnio, acelerador de hardware AI + projeto educacional schoolMIPS) e FSUE NPTSAP(departamento de Roscosmos), empresas americanas MIPS, Juniper Networks e AMD. Publicou um livro didático DMK-Press.Elaborei um plano para o laboratório e atraí autores de projetos educacionais anteriores, após o que transferi o controle para Alexander Romanov, que realizou um trabalho minucioso, gerenciando o projeto por quase dois anos. A criação do livro didático naturalmente se encaixa nas atividades de Alexander , que por 3 anos criou o laboratório no HSE MIEM , que lida com computadores embarcados, robótica e FPGAs. O laboratório organizou várias equipes no Innovate FPGA, uma das quais se tornou medalhista de bronze nas finais regionais.O livro não é apenas adequado para estudantes - pode ser usado em acampamentos de verão de design digital para estudantes avançados. Noções básicas sobre tutoriais na Internet do zero sobre como trabalhar com o ambiente Intel Quartus II não é trivial. E no livro está tudo descrito em etapas. Além disso, possui toda a base teórica para fazer algo interessante para as crianças em idade escolar, além de luzes piscantes que as incomodam rapidamente. Interessante é, por exemplo, um videogame: A idéia de aprender verilo através de jogos VGA não é nova - muitas universidades têm um laboratório assim, por exemplo, no Laboratório de Sistemas Digitais Introdutório do Instituto de Tecnologia de Massachusetts (MIT) 6.111. Além disso, há dois anos, foi publicado o livro Designing Video Game Hardware in Verilog Paperback, de Steven Hugg, com jogos bastante desenvolvidos com tanques, carros de corrida, um gerador de céu estrelado pseudo-aleatório usando LFSR, um buffer de quadro e até uma interface de software e hardware. Além disso, os jogos VGA são demos dos fabricantes dos FPGAs Xilinx e Intel / Altera, mais precisamente das empresas parceiras - Digilent e Terasic.

A idéia de aprender verilo através de jogos VGA não é nova - muitas universidades têm um laboratório assim, por exemplo, no Laboratório de Sistemas Digitais Introdutório do Instituto de Tecnologia de Massachusetts (MIT) 6.111. Além disso, há dois anos, foi publicado o livro Designing Video Game Hardware in Verilog Paperback, de Steven Hugg, com jogos bastante desenvolvidos com tanques, carros de corrida, um gerador de céu estrelado pseudo-aleatório usando LFSR, um buffer de quadro e até uma interface de software e hardware. Além disso, os jogos VGA são demos dos fabricantes dos FPGAs Xilinx e Intel / Altera, mais precisamente das empresas parceiras - Digilent e Terasic. Em particular, no laboratório do MITé mostrado claramente que tudo o que você precisa fazer para desenhar na tela é implementar na forma de diagrama uma função que toma as coordenadas X e Y de um ponto na tela como argumento e retorna a cor desse ponto (RGB). No caso mais simples, essa função é uma função combinada, por exemplo, uma função que chamará a obra-prima de Malevich: “a cor é preta (RGB = 0,0,0) se x> = 200 ex x <= 400 e y> = 200 e y <400, caso contrário branco (RGB = 1,1,1). " Além disso, chamaremos esse circuito de “misturador”, pois ele “misturará” entradas de geradores de imagens diferentes.Para gerar os argumentos do misturador X e Y, é usado um circuito simples de dois contadores que usa o sinal do relógio CLK. Além das coordenadas X e Y, este circuito também gera sinais HSYNC e VSYNC para o monitor VGA. Os sinais HSYNC e VSYNC permanecem desde o tempo do tubo de raios catódicos. Eles informam ao feixe virtual quando mover para o próximo ponto / pixel na tela horizontalmente e depois para a próxima linha verticalmente.Em um caso difícil, o mixer usa não apenas os valores de suas entradas X e Y, mas também os valores dos elementos de estado (D-flip-flops e memória), que são gravados usando o sinal do relógio CLK. Nesse caso, o relógio também entra no mixer. Os circuitos com sinais de relógio e elementos de estado são chamados seqüenciais (esses circuitos passam por uma sequência de estados que pulsa claramente um sinal de relógio pulsante). Nos misturadores sequenciais, você pode implementar imagens em movimento de qualquer grau de complexidade.Aqui estão as fotos do laboratório MIT shnaya (o mesmo está no monte de outras universidades) ilustrando a função do gerador HSYNC / VSYNC, o mixer (da mesma unidade que calcula RGB como uma função de X / HCOUNT e Y / VCOUNT), bem como a saída de HSYNC, VSYNC e RGB na tela. A imagem usa um comutador / multiplexador entre três misturadores - um desenha listras, outro desenha um retângulo e o terceiro desenha uma imagem na tela enquanto joga pingue-pongue:

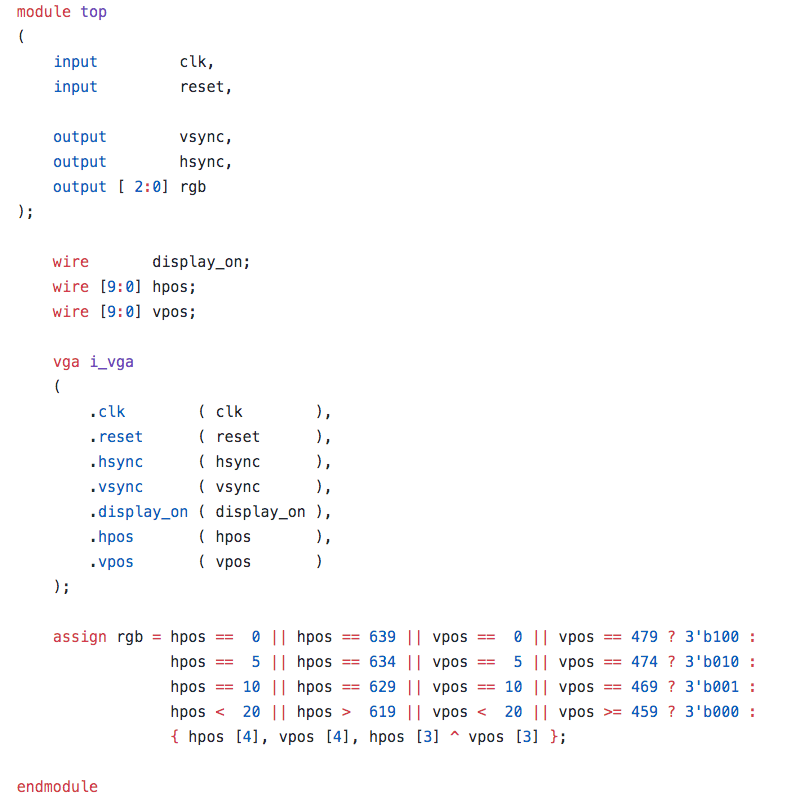

Em particular, no laboratório do MITé mostrado claramente que tudo o que você precisa fazer para desenhar na tela é implementar na forma de diagrama uma função que toma as coordenadas X e Y de um ponto na tela como argumento e retorna a cor desse ponto (RGB). No caso mais simples, essa função é uma função combinada, por exemplo, uma função que chamará a obra-prima de Malevich: “a cor é preta (RGB = 0,0,0) se x> = 200 ex x <= 400 e y> = 200 e y <400, caso contrário branco (RGB = 1,1,1). " Além disso, chamaremos esse circuito de “misturador”, pois ele “misturará” entradas de geradores de imagens diferentes.Para gerar os argumentos do misturador X e Y, é usado um circuito simples de dois contadores que usa o sinal do relógio CLK. Além das coordenadas X e Y, este circuito também gera sinais HSYNC e VSYNC para o monitor VGA. Os sinais HSYNC e VSYNC permanecem desde o tempo do tubo de raios catódicos. Eles informam ao feixe virtual quando mover para o próximo ponto / pixel na tela horizontalmente e depois para a próxima linha verticalmente.Em um caso difícil, o mixer usa não apenas os valores de suas entradas X e Y, mas também os valores dos elementos de estado (D-flip-flops e memória), que são gravados usando o sinal do relógio CLK. Nesse caso, o relógio também entra no mixer. Os circuitos com sinais de relógio e elementos de estado são chamados seqüenciais (esses circuitos passam por uma sequência de estados que pulsa claramente um sinal de relógio pulsante). Nos misturadores sequenciais, você pode implementar imagens em movimento de qualquer grau de complexidade.Aqui estão as fotos do laboratório MIT shnaya (o mesmo está no monte de outras universidades) ilustrando a função do gerador HSYNC / VSYNC, o mixer (da mesma unidade que calcula RGB como uma função de X / HCOUNT e Y / VCOUNT), bem como a saída de HSYNC, VSYNC e RGB na tela. A imagem usa um comutador / multiplexador entre três misturadores - um desenha listras, outro desenha um retângulo e o terceiro desenha uma imagem na tela enquanto joga pingue-pongue: no código, o misturador mais simples se parece com isso. Ele desenha quadrados multicoloridos a partir de misturas de vermelho, azul e verde, além de linhas de cores puras:

no código, o misturador mais simples se parece com isso. Ele desenha quadrados multicoloridos a partir de misturas de vermelho, azul e verde, além de linhas de cores puras: dessa maneira, você pode desenhar uma variedade de imagens estáticas coloridas. Aqui estão as imagens que os alunos pintaram em uma escola de verão em Zelenograd, imediatamente após uma breve palestra explicando como fazê-lo:

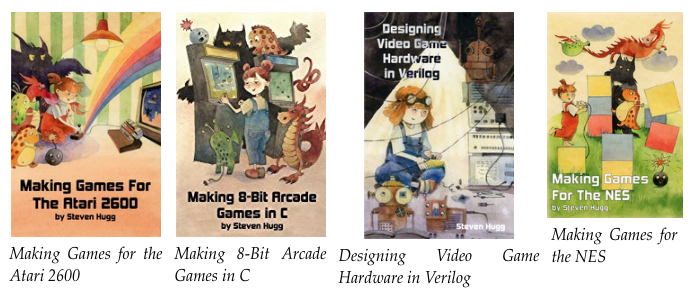

dessa maneira, você pode desenhar uma variedade de imagens estáticas coloridas. Aqui estão as imagens que os alunos pintaram em uma escola de verão em Zelenograd, imediatamente após uma breve palestra explicando como fazê-lo: Bem, as crianças em idade escolar podem codificar a função RGB (X, Y) e desenhar imagens estáticas. Mas o que fazer a seguir, qual é o próximo passo? Examinamos a possibilidade de usar materiais do MIT, Digilent + Xilinx, Altera + Terasic e Steven Hugg, após o que chegamos à conclusão de que eles não podem ser usados em sua forma pura. Os laboratórios da universidade estão incluídos no programa da universidade, e os materiais dos fornecedores do FPGA não são bem escritos e também não contêm dicas sobre como alterar o código no formato de uma escola de verão para que os alunos inventem seus jogos. O livro de Stephen Hugg tem duas desvantagens que são o outro lado de suas virtudes (vivacidade e colorido):Em geral, o verilog de Stephen Hugg se equipara à programação dos processadores dos antigos consoles de 8 bits da Atari e da Nintendo. Portanto, Hugg não está focado em treinar futuros super designers, mas em nostálgicos, cientistas da computação retro e outros reenactors. A diferença entre o ambiente e as ferramentas profissionais de design é ainda maior do que entre o ambiente de programação do Arduino e os kits de ferramentas do STM32.

Bem, as crianças em idade escolar podem codificar a função RGB (X, Y) e desenhar imagens estáticas. Mas o que fazer a seguir, qual é o próximo passo? Examinamos a possibilidade de usar materiais do MIT, Digilent + Xilinx, Altera + Terasic e Steven Hugg, após o que chegamos à conclusão de que eles não podem ser usados em sua forma pura. Os laboratórios da universidade estão incluídos no programa da universidade, e os materiais dos fornecedores do FPGA não são bem escritos e também não contêm dicas sobre como alterar o código no formato de uma escola de verão para que os alunos inventem seus jogos. O livro de Stephen Hugg tem duas desvantagens que são o outro lado de suas virtudes (vivacidade e colorido):Em geral, o verilog de Stephen Hugg se equipara à programação dos processadores dos antigos consoles de 8 bits da Atari e da Nintendo. Portanto, Hugg não está focado em treinar futuros super designers, mas em nostálgicos, cientistas da computação retro e outros reenactors. A diferença entre o ambiente e as ferramentas profissionais de design é ainda maior do que entre o ambiente de programação do Arduino e os kits de ferramentas do STM32. É claro que não proponho culpar o Cadence SimVision e o Synopsys Design Compiler por crianças em idade escolar por centenas de milhares de dólares, mas os alunos podem extrair versões gratuitas das ferramentas profissionais Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim e Icarus Verilog, GTKWave e o edaplayground online . com .Reli o parágrafo anterior e pensei: mas o Cadence SimVision para a escola de verão em Zelenograd poderia ter sido usado. Torna-se melhor e mais conveniente, tanto do seu concorrente direto Synopsys Design Vision Environment (DVE) * , quanto dos fundos da Mentor Graphics (ModelSim gratuito e Questa pago) e todas as ferramentas gratuitas e baratas (IcarusVerilog, etc.) Se a filial de Cadence em Moscou O Design System nos dará o direito e o suporte para usar seu software nas escolas de verão em Zelenograd. Pessoalmente, estarei por integrar isso no currículo da escola.* Para DVE, por exemplo, o texto na janela de origem é buggy / jumping quando eu o executo no Ubuntu. Eu tenho que fazer o redimensionamento da janela até que deixe de falhar. O SimVision não possui isso.Aqui está o início do tutorial da SimVision (22 vídeos no total):Mas voltando aos jogos. Se não for Stephen Hugg, então o que? Eu escrevi um exemplo de um jogo simples que usei em uma escola de verão em Zelenograd . As fontes do jogo estão no github . Se parece com isso:Por duas semanas, os alunos descobriram os princípios básicos do design no nível das transferências de registros e começaram a criar seus próprios jogos não triviais:Vamos falar sobre os detalhes técnicos de um exemplo de jogo. Um módulo de jogo independente de plataforma pode ser colocado (instanciado) no invólucro de qualquer placa FPGA que possua uma porta VGA e dois botões. Se a placa estiver completamente vazia, você poderá conectar um adaptador para VGA e botões através dos fios GPIO (entrada / saída de uso geral). O módulo do jogo consiste em:

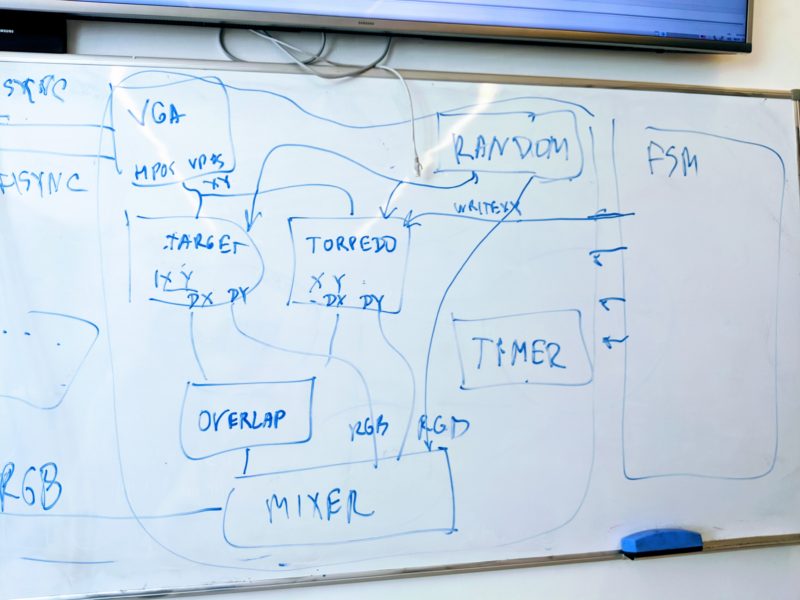

É claro que não proponho culpar o Cadence SimVision e o Synopsys Design Compiler por crianças em idade escolar por centenas de milhares de dólares, mas os alunos podem extrair versões gratuitas das ferramentas profissionais Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim e Icarus Verilog, GTKWave e o edaplayground online . com .Reli o parágrafo anterior e pensei: mas o Cadence SimVision para a escola de verão em Zelenograd poderia ter sido usado. Torna-se melhor e mais conveniente, tanto do seu concorrente direto Synopsys Design Vision Environment (DVE) * , quanto dos fundos da Mentor Graphics (ModelSim gratuito e Questa pago) e todas as ferramentas gratuitas e baratas (IcarusVerilog, etc.) Se a filial de Cadence em Moscou O Design System nos dará o direito e o suporte para usar seu software nas escolas de verão em Zelenograd. Pessoalmente, estarei por integrar isso no currículo da escola.* Para DVE, por exemplo, o texto na janela de origem é buggy / jumping quando eu o executo no Ubuntu. Eu tenho que fazer o redimensionamento da janela até que deixe de falhar. O SimVision não possui isso.Aqui está o início do tutorial da SimVision (22 vídeos no total):Mas voltando aos jogos. Se não for Stephen Hugg, então o que? Eu escrevi um exemplo de um jogo simples que usei em uma escola de verão em Zelenograd . As fontes do jogo estão no github . Se parece com isso:Por duas semanas, os alunos descobriram os princípios básicos do design no nível das transferências de registros e começaram a criar seus próprios jogos não triviais:Vamos falar sobre os detalhes técnicos de um exemplo de jogo. Um módulo de jogo independente de plataforma pode ser colocado (instanciado) no invólucro de qualquer placa FPGA que possua uma porta VGA e dois botões. Se a placa estiver completamente vazia, você poderá conectar um adaptador para VGA e botões através dos fios GPIO (entrada / saída de uso geral). O módulo do jogo consiste em:- Gerador de varredura VGA.

- Dois módulos de trabalho paralelos para torpedos de sprite e alvos de sprite.

- A máquina de estado para o cenário do jogo, com os estados "início", "orientação", "moscas", "vitória / derrota".

- Um módulo que determina se os sprites colidiram.

- Um cronômetro para definir a duração do efeito visual após a vitória (tela framboesa piscando) ou derrota (tela amarela).

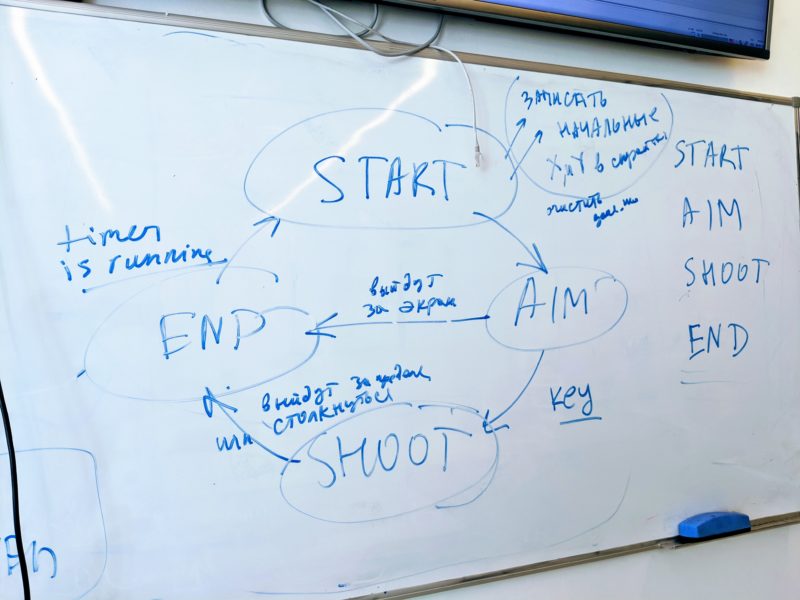

Para a próxima escola, todas essas imagens precisam ser redesenhadas usando draw.io ou Lucidchart em diagramas normais de microarquitetura: Você

Para a próxima escola, todas essas imagens precisam ser redesenhadas usando draw.io ou Lucidchart em diagramas normais de microarquitetura: Você também precisa adicionar aos materiais escolares diagramas de tempo desenhados usando WaveDrom para mostrar como o gerador de varredura VGA funciona e como o minipoduto calcula as coordenadas caminho de dados dentro de sprites:

também precisa adicionar aos materiais escolares diagramas de tempo desenhados usando WaveDrom para mostrar como o gerador de varredura VGA funciona e como o minipoduto calcula as coordenadas caminho de dados dentro de sprites: E é claro que você precisa desenhar diagramas da máquina de estados finitos. Eu fiz uma dúzia de variantes da máquina de estados finitos deste jogo, aqui no tabuleiro há uma variante com quatro estados:

E é claro que você precisa desenhar diagramas da máquina de estados finitos. Eu fiz uma dúzia de variantes da máquina de estados finitos deste jogo, aqui no tabuleiro há uma variante com quatro estados: Por que eu fiz muitas escolhas? Mesmo com uma máquina tão simples, você pode comparar diferentes estilos de codificação em um verbo, além de ilustrar a otimização de estados e tempos. Tudo isso é solicitado em uma entrevista para uma posição como designer de chips na Apple, NVidia, Intel, AMD e outras empresas. Portanto, essa área deve ser conhecida para que os dentes saltem. Existem alguns bons artigos de Clifford Cummings sobre esse assunto:

Por que eu fiz muitas escolhas? Mesmo com uma máquina tão simples, você pode comparar diferentes estilos de codificação em um verbo, além de ilustrar a otimização de estados e tempos. Tudo isso é solicitado em uma entrevista para uma posição como designer de chips na Apple, NVidia, Intel, AMD e outras empresas. Portanto, essa área deve ser conhecida para que os dentes saltem. Existem alguns bons artigos de Clifford Cummings sobre esse assunto:- Artigo mais recente de 2019: Design e síntese de FiniteStateMachine (FSM) usando SystemVerilog - Parte I por Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

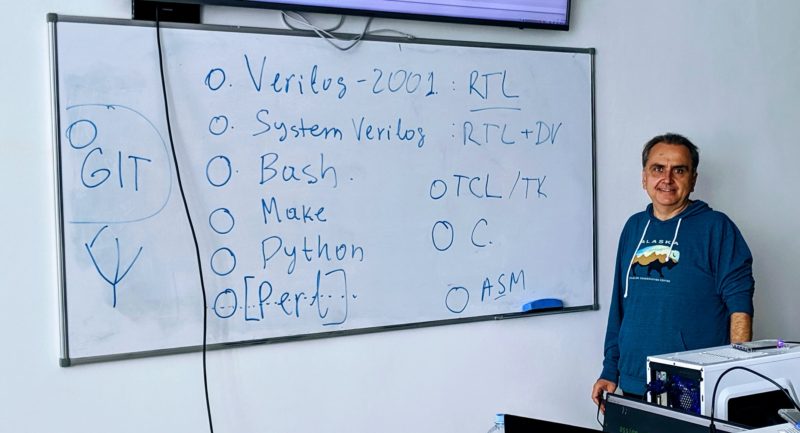

Sintetizei diferentes versões da máquina de estado do jogo usando a ferramenta Synopsys Design Compiler mais popular do setor e fiz um tablet assim. Como podemos ver, a versão moderna do DC otimiza todos os estilos com muita eficiência, portanto, é possível puxar picossegundos em máquinas de estado, mas não é necessário. Embora seja possível para máquinas de estado finito mais complexas, os truques dos artigos de Cummings serão mais críticos: durante a escola em Zelenograd, também discutimos que no design de chips, além das linguagens de descrição dos equipamentos Verilog e VHDL, muitas linguagens auxiliares são usadas:

durante a escola em Zelenograd, também discutimos que no design de chips, além das linguagens de descrição dos equipamentos Verilog e VHDL, muitas linguagens auxiliares são usadas:O Python é usado para automatizar montagem, gerenciamento de regressão e extrair informações de relatórios de síntese e geração de código, além de bash, make e outras cozinhas Unix / Linux.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ e bibliotecas como SystemC são usadas para escrever modelos de blocos de hardware no nível da transação. Os engenheiros de verificação verificam os blocos projetados no veril em relação a esses modelos.

Se você trabalha para uma empresa de processadores, é bom conhecer o montador. Mesmo que você não seja um programador de baixo nível e nem um verificador, mas um designer de processador no nível de transferências de registradores (Register Transfer Level - RTL).

Aqui estão os links para os interessados em usar o pearl como pré-processador para o verilogue:- G. Spivey. EP3: Um pré-processador Perl extensível

- Página de manual do vpp.pl

- Um pré-processador Verilog

Um exemplo de como usar o verlog pearl embutido para conectar 64 portas://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Seria bom se alguém escrevesse scripts universais para modelar e sintetizar um exemplo (não necessariamente meu jogo) em todas as principais plataformas de síntese, simulação, depuração, análise de consumo dinâmico de energia, design físico, ligação para todas as placas, etc. Isso pode ser usado em escolas e seminários:

Seria bom se alguém escrevesse scripts universais para modelar e sintetizar um exemplo (não necessariamente meu jogo) em todas as principais plataformas de síntese, simulação, depuração, análise de consumo dinâmico de energia, design físico, ligação para todas as placas, etc. Isso pode ser usado em escolas e seminários: Aqui você pode ter uma pergunta: por que uso os seminários sobre Linux? Embora o Windows também tenha um ambiente de modelagem e síntese para FPGAs, o Windows não se enraizou no setor de design de chips de massa. No início dos anos 90, o mercado de estações de trabalho para desenvolvedores ASIC foi dividido entre SunOS e HP / UX. Em seguida, as empresas eletrônicas tocaram por três anos no Windows NT, mas não funcionou. Depois disso, a Synopsys e outras empresas de software de design cuspiram e mudaram para o Linux - primeiro no Red Hat, depois no SuSE e Ubuntu. Eu suspeito, principalmente por causa de um monte de scripts no pearl, C-shell, etc., bem como por causa do trabalho remoto dos desenvolvedores através do telnet e do X Window.Portanto, nos meus seminários, eu vou com um monte de SSDs inicializáveis com o Lubuntu, nos quais todo o software necessário está instalado. Eu uso a inicialização herdada, mas recentemente descobriu-se que mais e mais computadores exigem a inicialização UEFI. Aparentemente, você precisará criar um SSD inicializável com inicialização UEFI.Empresas em movimento rápido usam o CentOS em vez do Red Hat. Talvez muitas ferramentas de design estejam no Debian, mas eu não o testei.

Aqui você pode ter uma pergunta: por que uso os seminários sobre Linux? Embora o Windows também tenha um ambiente de modelagem e síntese para FPGAs, o Windows não se enraizou no setor de design de chips de massa. No início dos anos 90, o mercado de estações de trabalho para desenvolvedores ASIC foi dividido entre SunOS e HP / UX. Em seguida, as empresas eletrônicas tocaram por três anos no Windows NT, mas não funcionou. Depois disso, a Synopsys e outras empresas de software de design cuspiram e mudaram para o Linux - primeiro no Red Hat, depois no SuSE e Ubuntu. Eu suspeito, principalmente por causa de um monte de scripts no pearl, C-shell, etc., bem como por causa do trabalho remoto dos desenvolvedores através do telnet e do X Window.Portanto, nos meus seminários, eu vou com um monte de SSDs inicializáveis com o Lubuntu, nos quais todo o software necessário está instalado. Eu uso a inicialização herdada, mas recentemente descobriu-se que mais e mais computadores exigem a inicialização UEFI. Aparentemente, você precisará criar um SSD inicializável com inicialização UEFI.Empresas em movimento rápido usam o CentOS em vez do Red Hat. Talvez muitas ferramentas de design estejam no Debian, mas eu não o testei. Para os seminários, uso os quadros FPGA chineses, um dos quais é mantido em minhas mãos por uma garota de Novosibirsk, Natasha, que está organizando festas What-Where-When no Vale do Silício .

Para os seminários, uso os quadros FPGA chineses, um dos quais é mantido em minhas mãos por uma garota de Novosibirsk, Natasha, que está organizando festas What-Where-When no Vale do Silício . No mês de março, eu andei pela vida selvagem da Califórnia junto com o empresário russo Sergei Zorin, que levou uma dúzia de placas da ZEOWAA para Moscou, características semelhantes às que Natasha está segurando em suas mãos.Como provavelmente não haverá seminários em Zelenograd devido ao coronavírus neste verão, acho que darei essa dúzia de taxas a crianças em idade escolar de Moscou de graça (UPD: crianças em idade escolar de outras cidades também podem, embora haja um barulho adicional no encaminhamento). Com duas condições:

No mês de março, eu andei pela vida selvagem da Califórnia junto com o empresário russo Sergei Zorin, que levou uma dúzia de placas da ZEOWAA para Moscou, características semelhantes às que Natasha está segurando em suas mãos.Como provavelmente não haverá seminários em Zelenograd devido ao coronavírus neste verão, acho que darei essa dúzia de taxas a crianças em idade escolar de Moscou de graça (UPD: crianças em idade escolar de outras cidades também podem, embora haja um barulho adicional no encaminhamento). Com duas condições:Antes de adquirir uma placa, você precisa seguir as três partes do curso on-line "Como funcionam os criadores de nanochips inteligentes" ( "Do transistor ao microcircuito" , "O lado lógico do circuito digital" , "O lado físico do circuito digital" ) e obter um certificado. Criamos este curso em conjunto com RUSNANO, ou melhor, sua filha educacional eNano, o projeto STEMford.

, , , . , , , ( ) . , , .

, , .

Se você deseja comprar um novo livro "Síntese lógica" como um auxílio para esse projeto , para os leitores de Habr, ela tem um código promocional - Sintez_2020. No futuro, seria bom usar as placas chinesas e criar uma placa russa barata para esses exercícios com FPGA, com um design aberto. É bem-vindo se você compartilhar seus pensamentos nos comentários sobre o software de design do quadro e idéias sobre como melhor projetar e comercializar esse quadro. Para uso em massa com crianças em idade escolar, é desejável que não custe mais do que US $ 30 ou 2000 rublos.

No futuro, seria bom usar as placas chinesas e criar uma placa russa barata para esses exercícios com FPGA, com um design aberto. É bem-vindo se você compartilhar seus pensamentos nos comentários sobre o software de design do quadro e idéias sobre como melhor projetar e comercializar esse quadro. Para uso em massa com crianças em idade escolar, é desejável que não custe mais do que US $ 30 ou 2000 rublos. Se você é um estudante e está interessado no design de microcircuitos, pode acessar o MIET, HSE MIEM, Instituto de Física de Engenharia de Moscou, Universidade Estadual de Moscou, Instituto de Física e Tecnologia de Moscou ( Nikita Polyakov está envolvido em tais exercícios, MPEI, MISiS, ITMO, LETI, Universidade de Samara, algumas universidades ucranianas (KNU, Chernihiv NTU, Kharkov KNURE) e outras universidades. Então, eu descobri como minha abordagem do comitê de seleção do MIET em Zelenograd estava sendo reparada:

Se você é um estudante e está interessado no design de microcircuitos, pode acessar o MIET, HSE MIEM, Instituto de Física de Engenharia de Moscou, Universidade Estadual de Moscou, Instituto de Física e Tecnologia de Moscou ( Nikita Polyakov está envolvido em tais exercícios, MPEI, MISiS, ITMO, LETI, Universidade de Samara, algumas universidades ucranianas (KNU, Chernihiv NTU, Kharkov KNURE) e outras universidades. Então, eu descobri como minha abordagem do comitê de seleção do MIET em Zelenograd estava sendo reparada: mas aqui está como o MIET olha para dentro: você pode

mas aqui está como o MIET olha para dentro: você pode encontrar um emprego ali mesmo em frente ao MIET para a ONG ELVIS, que lida com câmeras inteligentes e chips de satélite:

encontrar um emprego ali mesmo em frente ao MIET para a ONG ELVIS, que lida com câmeras inteligentes e chips de satélite: ou você pode vir para o Vale do Silício. Deseja obter uma entrevista com Dolina? Pratique em placas FPGA!

ou você pode vir para o Vale do Silício. Deseja obter uma entrevista com Dolina? Pratique em placas FPGA!