Laboratorium Sintesis Digital yang baru melanjutkan tradisi tutorial David Harris dan Sarah Harris, Sirkuit Digital dan Arsitektur Komputer, yang mengunduh situs Inggris . Laboratorium memungkinkan Anda menyentuh keseluruhan teori Harris & Harris di papan FPGA, dari lampu yang berkedip hingga prosesor. Konsep pemrosesan konveyor juga dianalisis di laboratorium, tanpanya Anda tidak akan lulus wawancara untuk bekerja sebagai perancang di perusahaan mikroelektronika mana pun. Pada akhirnya, jalur dari FPGA ke ASIC, sirkuit masal yang ada di iPhone, Tesla dan akselerator AI.Buku itu berisi wawancara dengan tim dari St. Petersburg yang dibawa Intel ke kantor pusatnya di Silicon Valley untuk kemenangan mereka dalam kontes Innovate FPGA. Buku "Sintesis Digital: Kursus Praktis"Cadence Design Systems, sebuah perusahaan terkemuka dalam otomatisasi desain chip, didukung (dalam foto di atas, Siberian Natasha berdiri dengan papan FPGA di depan markas Cadence di Silicon Valley - videonya akan ada di pos).Labnik diciptakan di bawah naungan Sekolah Tinggi Ekonomi / MIEM (Alexander Romanov, Veronika Prokhorova, dan Igor Agamirzyan), sementara berbagai bab ditulis oleh para guru dari Moskow, Kiev dan Universitas Samara, St. Petersburg ITMO, Politeknik Chernihiv, dan Universitas California Santa Cruz ( Charles Danchek , kantor malam di Lembah Silikon). Penciptaan buku teks ini dihadiri oleh insinyur dari perusahaan Rusia IVA Technologies (Stanislav Zhelnio, akselerator perangkat keras AI + sekolah proyek pendidikan) dan FSUE NPTSAP(departemen Roscosmos), MIPS perusahaan Amerika, Juniper Networks dan AMD. Menerbitkan buku teks DMK-Press.Saya menyusun rencana untuk laboratorium dan menarik penulis dari proyek pendidikan sebelumnya, setelah itu saya mentransfer kendali ke Alexander Romanov, yang melakukan pekerjaan yang melelahkan, mengelola proyek selama hampir dua tahun. Penciptaan buku teks secara alami sesuai dengan kegiatan Alexander , yang selama 3 tahun mengangkat laboratorium di HSE MIEM , yang berkaitan dengan komputer tertanam, robot, dan FPGA. Laboratorium ini mengorganisasi beberapa tim di Innovate FPGA, yang salah satunya menjadi peraih medali perunggu di putaran final regional.Buku teks ini tidak hanya cocok untuk siswa - buku ini dapat digunakan untuk perkemahan musim panas desain digital untuk siswa tingkat lanjut. Memahami tutorial di Internet dari awal tentang cara bekerja dengan lingkungan Intel Quartus II bukanlah hal sepele. Dan di buku teks semuanya dijelaskan dalam langkah-langkah. Selain itu, ia memiliki semua landasan teori untuk melakukan sesuatu yang menarik bagi anak sekolah, selain lampu berkedip yang dengan cepat mengganggu mereka. Yang menarik misalnya adalah video game:

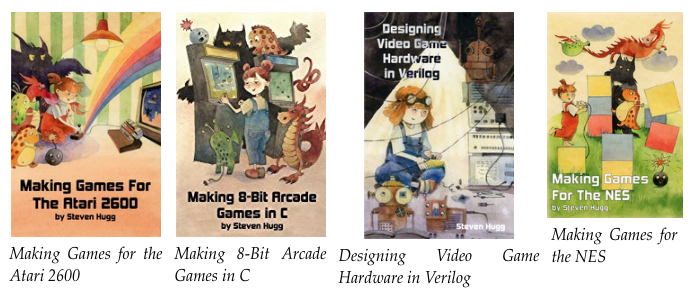

Laboratorium Sintesis Digital yang baru melanjutkan tradisi tutorial David Harris dan Sarah Harris, Sirkuit Digital dan Arsitektur Komputer, yang mengunduh situs Inggris . Laboratorium memungkinkan Anda menyentuh keseluruhan teori Harris & Harris di papan FPGA, dari lampu yang berkedip hingga prosesor. Konsep pemrosesan konveyor juga dianalisis di laboratorium, tanpanya Anda tidak akan lulus wawancara untuk bekerja sebagai perancang di perusahaan mikroelektronika mana pun. Pada akhirnya, jalur dari FPGA ke ASIC, sirkuit masal yang ada di iPhone, Tesla dan akselerator AI.Buku itu berisi wawancara dengan tim dari St. Petersburg yang dibawa Intel ke kantor pusatnya di Silicon Valley untuk kemenangan mereka dalam kontes Innovate FPGA. Buku "Sintesis Digital: Kursus Praktis"Cadence Design Systems, sebuah perusahaan terkemuka dalam otomatisasi desain chip, didukung (dalam foto di atas, Siberian Natasha berdiri dengan papan FPGA di depan markas Cadence di Silicon Valley - videonya akan ada di pos).Labnik diciptakan di bawah naungan Sekolah Tinggi Ekonomi / MIEM (Alexander Romanov, Veronika Prokhorova, dan Igor Agamirzyan), sementara berbagai bab ditulis oleh para guru dari Moskow, Kiev dan Universitas Samara, St. Petersburg ITMO, Politeknik Chernihiv, dan Universitas California Santa Cruz ( Charles Danchek , kantor malam di Lembah Silikon). Penciptaan buku teks ini dihadiri oleh insinyur dari perusahaan Rusia IVA Technologies (Stanislav Zhelnio, akselerator perangkat keras AI + sekolah proyek pendidikan) dan FSUE NPTSAP(departemen Roscosmos), MIPS perusahaan Amerika, Juniper Networks dan AMD. Menerbitkan buku teks DMK-Press.Saya menyusun rencana untuk laboratorium dan menarik penulis dari proyek pendidikan sebelumnya, setelah itu saya mentransfer kendali ke Alexander Romanov, yang melakukan pekerjaan yang melelahkan, mengelola proyek selama hampir dua tahun. Penciptaan buku teks secara alami sesuai dengan kegiatan Alexander , yang selama 3 tahun mengangkat laboratorium di HSE MIEM , yang berkaitan dengan komputer tertanam, robot, dan FPGA. Laboratorium ini mengorganisasi beberapa tim di Innovate FPGA, yang salah satunya menjadi peraih medali perunggu di putaran final regional.Buku teks ini tidak hanya cocok untuk siswa - buku ini dapat digunakan untuk perkemahan musim panas desain digital untuk siswa tingkat lanjut. Memahami tutorial di Internet dari awal tentang cara bekerja dengan lingkungan Intel Quartus II bukanlah hal sepele. Dan di buku teks semuanya dijelaskan dalam langkah-langkah. Selain itu, ia memiliki semua landasan teori untuk melakukan sesuatu yang menarik bagi anak sekolah, selain lampu berkedip yang dengan cepat mengganggu mereka. Yang menarik misalnya adalah video game: Gagasan belajar verilo melalui game VGA bukanlah hal baru - banyak universitas memiliki lab seperti itu, misalnya, di Massachusetts Institute of Technology (MIT) 6.111 Laboratorium Sistem Digital Pengantar. Juga, dua tahun lalu, buku Merancang Video Game Hardware di Verilog Paperback oleh Steven Hugg diterbitkan, dengan game yang cukup berkembang dengan tank, mobil balap, generator langit berbintang pseudo-acak menggunakan LFSR, penyangga bingkai, dan bahkan antarmuka perangkat keras-perangkat lunak. Selain itu, game VGA dalam demo dari produsen FPGA Xilinx dan Intel / Altera, lebih tepatnya dari perusahaan mitra mereka - Digilent dan Terasic.

Gagasan belajar verilo melalui game VGA bukanlah hal baru - banyak universitas memiliki lab seperti itu, misalnya, di Massachusetts Institute of Technology (MIT) 6.111 Laboratorium Sistem Digital Pengantar. Juga, dua tahun lalu, buku Merancang Video Game Hardware di Verilog Paperback oleh Steven Hugg diterbitkan, dengan game yang cukup berkembang dengan tank, mobil balap, generator langit berbintang pseudo-acak menggunakan LFSR, penyangga bingkai, dan bahkan antarmuka perangkat keras-perangkat lunak. Selain itu, game VGA dalam demo dari produsen FPGA Xilinx dan Intel / Altera, lebih tepatnya dari perusahaan mitra mereka - Digilent dan Terasic. Secara khusus, di lab dari MITsangat jelas ditunjukkan bahwa semua yang perlu Anda lakukan untuk menggambar di layar adalah menerapkan dalam bentuk diagram fungsi yang mengambil koordinat X dan Y dari suatu titik di layar sebagai argumen dan mengembalikan warna titik itu (RGB). Dalam kasus paling sederhana, fungsi ini adalah fungsi kombinasi, misalnya, fungsi seperti itu akan menarik karya Malevich: “warna hitam (RGB = 0,0,0) jika x> = 200 dan x <= 400 dan y> = 200 dan y <400, jika tidak putih (RGB = 1,1,1). " Kami selanjutnya akan menyebut sirkuit seperti itu sebagai "mixer", karena itu akan "mencampur" input dari generator gambar yang berbeda.Untuk menghasilkan argumen mixer X dan Y sendiri, sirkuit dua-counter sederhana digunakan yang menggunakan sinyal clock CLK. Selain koordinat X dan Y, sirkuit ini juga menghasilkan sinyal HSYNC dan VSYNC untuk tampilan VGA. Sinyal HSYNC dan VSYNC tetap sejak zaman tabung sinar katoda. Mereka memberi tahu balok virtual kapan harus pindah ke titik / piksel berikutnya pada layar secara horizontal, dan kemudian ke baris berikutnya secara vertikal.Dalam kasus yang sulit, mixer tidak hanya menggunakan nilai input X dan Y, tetapi juga nilai dari elemen keadaan (D-flip-flop dan memori), yang direkam menggunakan sinyal clock CLK. Dalam hal ini, jam juga memasuki mixer. Sirkuit dengan sinyal clock dan elemen state disebut berurutan (sirkuit ini melewati urutan status yang secara jelas menggetarkan sinyal clock yang berdenyut). Pada mixer serial, Anda dapat menerapkan gambar bergerak dengan tingkat kerumitan apa pun.Berikut adalah gambar-gambar dari lab shnaya MIT (yang sama ada di tumpukan universitas lain) yang menggambarkan fungsi generator HSYNC / VSYNC, mixer (unit yang sama yang menghitung RGB sebagai fungsi X / HCOUNT dan Y / VCOUNT), serta output dari HSYNC, VSYNC dan RGB di layar. Gambar menggunakan switch / multiplexer antara tiga mixer - satu menggambar garis, yang lain menggambar persegi panjang, dan yang ketiga menggambar gambar di layar saat bermain ping pong:

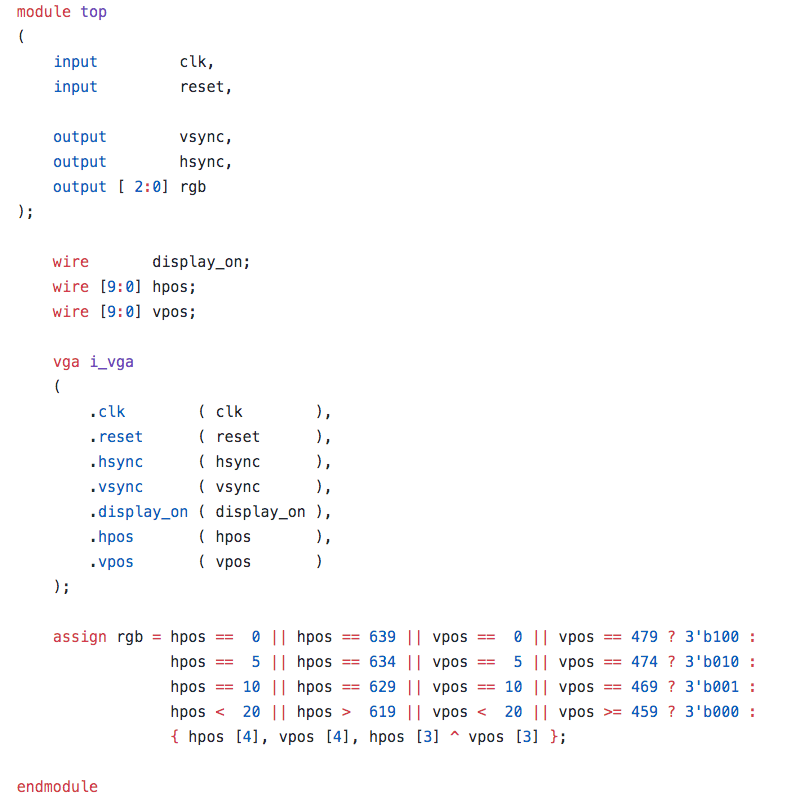

Secara khusus, di lab dari MITsangat jelas ditunjukkan bahwa semua yang perlu Anda lakukan untuk menggambar di layar adalah menerapkan dalam bentuk diagram fungsi yang mengambil koordinat X dan Y dari suatu titik di layar sebagai argumen dan mengembalikan warna titik itu (RGB). Dalam kasus paling sederhana, fungsi ini adalah fungsi kombinasi, misalnya, fungsi seperti itu akan menarik karya Malevich: “warna hitam (RGB = 0,0,0) jika x> = 200 dan x <= 400 dan y> = 200 dan y <400, jika tidak putih (RGB = 1,1,1). " Kami selanjutnya akan menyebut sirkuit seperti itu sebagai "mixer", karena itu akan "mencampur" input dari generator gambar yang berbeda.Untuk menghasilkan argumen mixer X dan Y sendiri, sirkuit dua-counter sederhana digunakan yang menggunakan sinyal clock CLK. Selain koordinat X dan Y, sirkuit ini juga menghasilkan sinyal HSYNC dan VSYNC untuk tampilan VGA. Sinyal HSYNC dan VSYNC tetap sejak zaman tabung sinar katoda. Mereka memberi tahu balok virtual kapan harus pindah ke titik / piksel berikutnya pada layar secara horizontal, dan kemudian ke baris berikutnya secara vertikal.Dalam kasus yang sulit, mixer tidak hanya menggunakan nilai input X dan Y, tetapi juga nilai dari elemen keadaan (D-flip-flop dan memori), yang direkam menggunakan sinyal clock CLK. Dalam hal ini, jam juga memasuki mixer. Sirkuit dengan sinyal clock dan elemen state disebut berurutan (sirkuit ini melewati urutan status yang secara jelas menggetarkan sinyal clock yang berdenyut). Pada mixer serial, Anda dapat menerapkan gambar bergerak dengan tingkat kerumitan apa pun.Berikut adalah gambar-gambar dari lab shnaya MIT (yang sama ada di tumpukan universitas lain) yang menggambarkan fungsi generator HSYNC / VSYNC, mixer (unit yang sama yang menghitung RGB sebagai fungsi X / HCOUNT dan Y / VCOUNT), serta output dari HSYNC, VSYNC dan RGB di layar. Gambar menggunakan switch / multiplexer antara tiga mixer - satu menggambar garis, yang lain menggambar persegi panjang, dan yang ketiga menggambar gambar di layar saat bermain ping pong: Dalam kode, mixer paling sederhana terlihat seperti ini. Dia menggambar kotak multi-warna dari campuran merah, biru dan hijau, serta garis-garis warna murni:

Dalam kode, mixer paling sederhana terlihat seperti ini. Dia menggambar kotak multi-warna dari campuran merah, biru dan hijau, serta garis-garis warna murni: Dengan cara ini, Anda dapat menggambar berbagai gambar statis berwarna-warni. Berikut adalah gambar-gambar yang dilukis siswa di sekolah musim panas di Zelenograd segera setelah ceramah singkat yang menjelaskan cara melakukannya:

Dengan cara ini, Anda dapat menggambar berbagai gambar statis berwarna-warni. Berikut adalah gambar-gambar yang dilukis siswa di sekolah musim panas di Zelenograd segera setelah ceramah singkat yang menjelaskan cara melakukannya: Nah, anak sekolah dapat menyandikan fungsi RGB (X, Y) dan menggambar gambar statis. Tapi apa yang harus dilakukan selanjutnya, apa langkah selanjutnya? Kami memeriksa kemungkinan menggunakan bahan dari MIT, Digilent + Xilinx, Altera + Terasic dan Steven Hugg, setelah itu kami sampai pada kesimpulan bahwa mereka tidak dapat digunakan dalam bentuk murni mereka. Laboratorium universitas termasuk dalam program universitas, dan materi dari vendor FPGA tidak ditulis dengan baik, dan juga tidak mengandung tips tentang cara mengubah kode dalam format sekolah musim panas sehingga siswa menciptakan permainan mereka. The book of Stephen Hugg memiliki dua kelemahan yang merupakan sandal sisi kebajikan (keaktifan dan colorfulness):Secara umum, Verilog di Stephen Hugg setara dengan pemrograman prosesor konsol 8-bit lama dari Atari dan Nintendo. Dengan demikian, Hugg tidak fokus pada pelatihan superdesigners masa depan, tetapi pada nostalgia, ilmuwan komputer retro dan reenactor lainnya. Perbedaan antara lingkungannya dan alat desain profesionalnya bahkan lebih besar daripada antara lingkungan pemrograman Arduino dan toolkit untuk STM32.

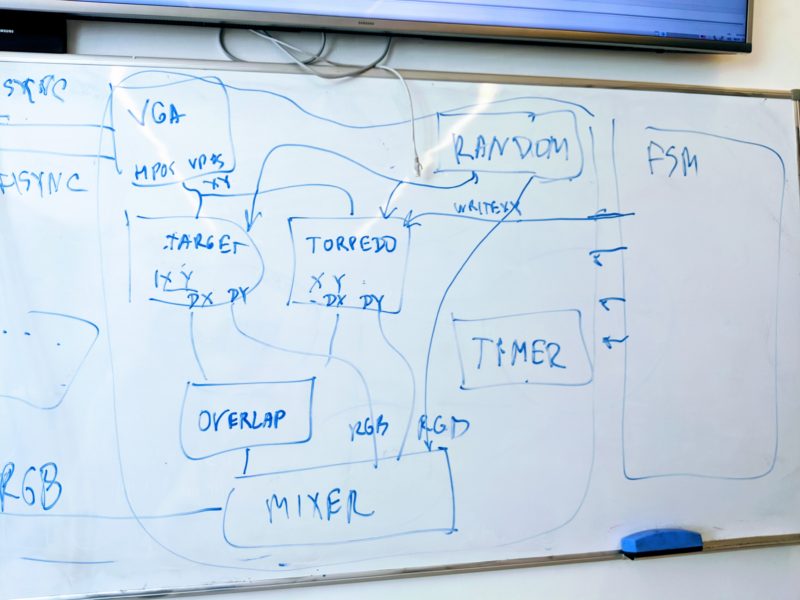

Nah, anak sekolah dapat menyandikan fungsi RGB (X, Y) dan menggambar gambar statis. Tapi apa yang harus dilakukan selanjutnya, apa langkah selanjutnya? Kami memeriksa kemungkinan menggunakan bahan dari MIT, Digilent + Xilinx, Altera + Terasic dan Steven Hugg, setelah itu kami sampai pada kesimpulan bahwa mereka tidak dapat digunakan dalam bentuk murni mereka. Laboratorium universitas termasuk dalam program universitas, dan materi dari vendor FPGA tidak ditulis dengan baik, dan juga tidak mengandung tips tentang cara mengubah kode dalam format sekolah musim panas sehingga siswa menciptakan permainan mereka. The book of Stephen Hugg memiliki dua kelemahan yang merupakan sandal sisi kebajikan (keaktifan dan colorfulness):Secara umum, Verilog di Stephen Hugg setara dengan pemrograman prosesor konsol 8-bit lama dari Atari dan Nintendo. Dengan demikian, Hugg tidak fokus pada pelatihan superdesigners masa depan, tetapi pada nostalgia, ilmuwan komputer retro dan reenactor lainnya. Perbedaan antara lingkungannya dan alat desain profesionalnya bahkan lebih besar daripada antara lingkungan pemrograman Arduino dan toolkit untuk STM32. Tentu saja, saya tidak bermaksud menyalahkan Cadence SimVision dan Synopsys Design Compiler untuk anak sekolah seharga ratusan ribu dolar, tetapi anak sekolah mungkin mendapatkan versi gratis alat profesional Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, serta Icarus Verilog, GTKWave dan edaplayground online . com .Saya membaca ulang paragraf dan pemikiran sebelumnya: tetapi Cadence SimVision untuk sekolah musim panas di Zelenograd bisa digunakan. Itu dibuat lebih baik dan lebih nyaman, baik dari pesaing langsungnya Synopsys Design Vision Environment (DVE) * , dan dana dari Mentor Graphics (ModelSim gratis dan Questa berbayar), dan semua alat murah dan gratis (IcarusVerilog, dll.) Jika cabang Irama Moskow Sistem Desain akan memberi kita hak dan dukungan untuk menggunakan perangkat lunak mereka di sekolah musim panas di Zelenograd, secara pribadi saya akan mengintegrasikannya ke dalam kurikulum sekolah.* Untuk DVE, misalnya, teks di jendela sumber buggy / jumping ketika saya menjalankannya di Ubuntu. Saya harus melakukan perubahan ukuran jendela hingga berhenti gagal. SimVision tidak memiliki ini.Inilah awal tutorial SimVision (total 22 video):Tapi kembali ke permainan. Jika bukan Stephen Hugg, lalu apa? Saya menulis contoh permainan sederhana yang saya gunakan di sekolah musim panas di Zelenograd . Sumber permainan ada di github . Ini terlihat seperti ini:Selama dua minggu, siswa menemukan prinsip-prinsip dasar desain pada tingkat transfer register dan mulai membuat permainan mereka sendiri, dan non-sepele:Mari kita bicara tentang detail teknis dari game contoh. Modul permainan platform-independen dapat ditempatkan (dipakai) di bungkus papan FPGA yang memiliki port VGA dan dua tombol. Jika papan benar-benar kosong, maka Anda dapat menghubungkan adaptor untuk VGA dan tombol untuk itu melalui kabel GPIO (input / output tujuan umum). Modul permainan terdiri dari:

Tentu saja, saya tidak bermaksud menyalahkan Cadence SimVision dan Synopsys Design Compiler untuk anak sekolah seharga ratusan ribu dolar, tetapi anak sekolah mungkin mendapatkan versi gratis alat profesional Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, serta Icarus Verilog, GTKWave dan edaplayground online . com .Saya membaca ulang paragraf dan pemikiran sebelumnya: tetapi Cadence SimVision untuk sekolah musim panas di Zelenograd bisa digunakan. Itu dibuat lebih baik dan lebih nyaman, baik dari pesaing langsungnya Synopsys Design Vision Environment (DVE) * , dan dana dari Mentor Graphics (ModelSim gratis dan Questa berbayar), dan semua alat murah dan gratis (IcarusVerilog, dll.) Jika cabang Irama Moskow Sistem Desain akan memberi kita hak dan dukungan untuk menggunakan perangkat lunak mereka di sekolah musim panas di Zelenograd, secara pribadi saya akan mengintegrasikannya ke dalam kurikulum sekolah.* Untuk DVE, misalnya, teks di jendela sumber buggy / jumping ketika saya menjalankannya di Ubuntu. Saya harus melakukan perubahan ukuran jendela hingga berhenti gagal. SimVision tidak memiliki ini.Inilah awal tutorial SimVision (total 22 video):Tapi kembali ke permainan. Jika bukan Stephen Hugg, lalu apa? Saya menulis contoh permainan sederhana yang saya gunakan di sekolah musim panas di Zelenograd . Sumber permainan ada di github . Ini terlihat seperti ini:Selama dua minggu, siswa menemukan prinsip-prinsip dasar desain pada tingkat transfer register dan mulai membuat permainan mereka sendiri, dan non-sepele:Mari kita bicara tentang detail teknis dari game contoh. Modul permainan platform-independen dapat ditempatkan (dipakai) di bungkus papan FPGA yang memiliki port VGA dan dua tombol. Jika papan benar-benar kosong, maka Anda dapat menghubungkan adaptor untuk VGA dan tombol untuk itu melalui kabel GPIO (input / output tujuan umum). Modul permainan terdiri dari:- Generator pindai VGA.

- Dua modul kerja paralel untuk torpedo sprite dan target sprite.

- Mesin negara untuk skenario permainan, dengan negara "mulai", "bimbingan", "lalat", "kemenangan / kekalahan".

- Modul yang menentukan apakah sprite bertabrakan.

- Pengatur waktu untuk mengatur durasi efek visual setelah menang (layar raspberry berkedip) atau kalah (layar kuning).

Untuk sekolah berikutnya, semua gambar ini perlu digambar ulang menggunakan draw.io atau Lucidchart ke dalam diagram mikroarsitektur normal: Anda

Untuk sekolah berikutnya, semua gambar ini perlu digambar ulang menggunakan draw.io atau Lucidchart ke dalam diagram mikroarsitektur normal: Anda juga perlu menambahkan garis waktu yang digambar dengan WaveDrom ke materi sekolah untuk menunjukkan cara kerja generator pemindaian VGA dan bagaimana pipa mini menghitung koordinat. jalur data di dalam sprite:

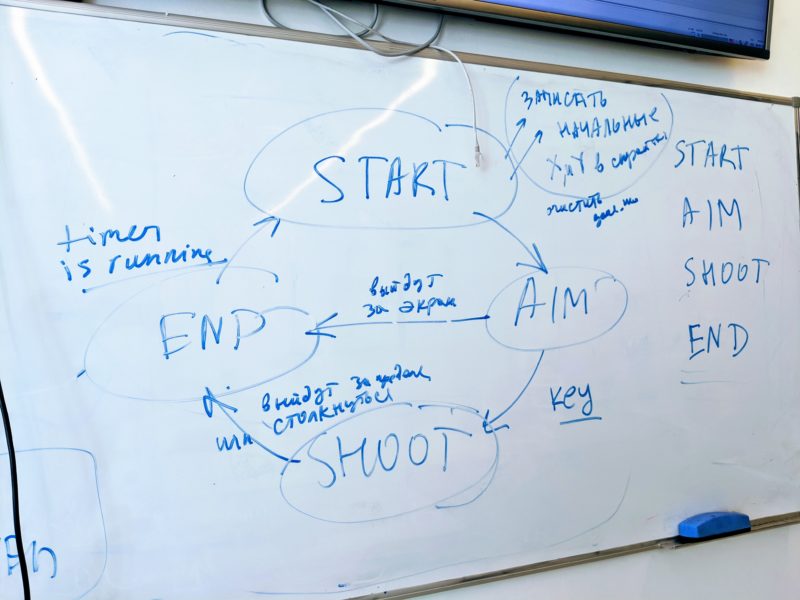

juga perlu menambahkan garis waktu yang digambar dengan WaveDrom ke materi sekolah untuk menunjukkan cara kerja generator pemindaian VGA dan bagaimana pipa mini menghitung koordinat. jalur data di dalam sprite: Dan tentu saja Anda perlu menggambar diagram dari mesin state hingga. Saya membuat selusin varian mesin negara terbatas dari permainan ini, di sini di papan ada varian dengan empat negara:

Dan tentu saja Anda perlu menggambar diagram dari mesin state hingga. Saya membuat selusin varian mesin negara terbatas dari permainan ini, di sini di papan ada varian dengan empat negara: Mengapa saya membuat banyak pilihan? Bahkan dengan mesin sederhana seperti itu, Anda dapat membandingkan berbagai gaya pengkodean pada veril, serta menggambarkan optimalisasi status dan waktu. Semua ini ditanyakan dalam wawancara untuk posisi sebagai desainer chip di Apple, NVidia, Intel, AMD dan perusahaan lain. Karena itu, area ini harus diketahui agar gigi memantul. Ada beberapa artikel Clifford Cummings yang bagus tentang hal ini:

Mengapa saya membuat banyak pilihan? Bahkan dengan mesin sederhana seperti itu, Anda dapat membandingkan berbagai gaya pengkodean pada veril, serta menggambarkan optimalisasi status dan waktu. Semua ini ditanyakan dalam wawancara untuk posisi sebagai desainer chip di Apple, NVidia, Intel, AMD dan perusahaan lain. Karena itu, area ini harus diketahui agar gigi memantul. Ada beberapa artikel Clifford Cummings yang bagus tentang hal ini:- 2019 Artikel Terbaru: Desain & Sintesis FiniteStateMachine (FSM) menggunakan SystemVerilog - Bagian I oleh Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

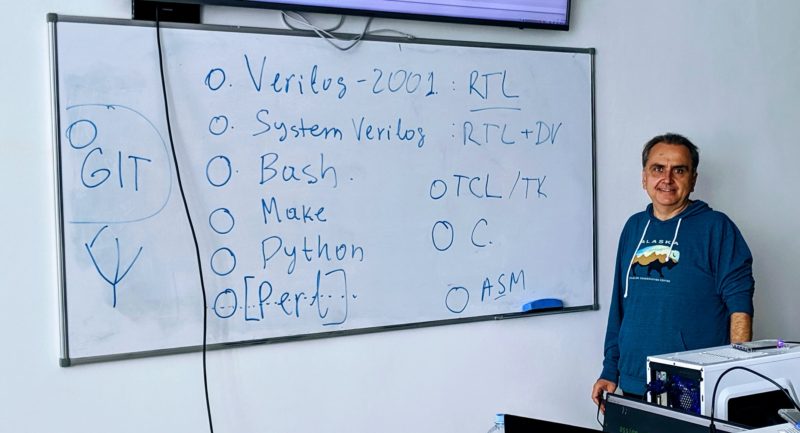

Saya mensintesis versi berbeda dari mesin negara permainan menggunakan alat Compops Desain Synopsys paling populer di industri dan membuat tablet seperti itu. Seperti yang dapat kita lihat, DC versi modern mengoptimalkan semua gaya dengan sangat efisien, jadi menarik picosecond pada mesin negara adalah mungkin, tetapi tidak perlu. Meskipun dimungkinkan untuk mesin negara berhingga yang lebih kompleks, trik dari artikel Cummings akan lebih kritis: Selama sekolah di Zelenograd, kami juga membahas bahwa dalam desain keripik, selain bahasa deskripsi peralatan Verilog dan VHDL, banyak bahasa tambahan digunakan:

Selama sekolah di Zelenograd, kami juga membahas bahwa dalam desain keripik, selain bahasa deskripsi peralatan Verilog dan VHDL, banyak bahasa tambahan digunakan:Python digunakan untuk mengotomatisasi perakitan, manajemen regresi, dan mengekstrak informasi dari sintesis dan laporan pembuatan kode, serta bash, make, dan dapur Unix / Linux lainnya.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ dan perpustakaan seperti SystemC digunakan untuk menulis model blok perangkat keras tingkat transaksi. Teknisi verifikasi memeriksa blok yang dirancang pada veril terhadap model-model ini.

Jika Anda bekerja untuk perusahaan prosesor, ada baiknya Anda mengenal assembler. Sekalipun Anda bukan pemrogram tingkat rendah dan bukan pemverifikasi, tetapi perancang prosesor pada tingkat transfer register (Register Transfer Level - RTL).

Berikut ini tautan untuk mereka yang tertarik menggunakan mutiara sebagai preprosesor untuk Verilog:- G. Spivey. EP3: Sebuah preprosesor Perl yang dapat diperpanjang

- halaman manual vpp.pl

- Preprocessor Verilog

Contoh cara menggunakan mutiara verlog bawaan untuk menghubungkan 64 port://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Akan lebih baik jika seseorang menulis skrip universal untuk memodelkan dan mensintesiskan sebuah contoh (belum tentu permainan saya) pada semua platform utama untuk sintesis, simulasi, debugging, analisis konsumsi daya dinamis, desain fisik, penjilidan untuk semua papan, dll. Ini dapat digunakan di sekolah dan seminar:

Akan lebih baik jika seseorang menulis skrip universal untuk memodelkan dan mensintesiskan sebuah contoh (belum tentu permainan saya) pada semua platform utama untuk sintesis, simulasi, debugging, analisis konsumsi daya dinamis, desain fisik, penjilidan untuk semua papan, dll. Ini dapat digunakan di sekolah dan seminar: Di sini Anda mungkin memiliki pertanyaan: mengapa saya menggunakan seminar Linux? Meskipun Windows juga memiliki lingkungan pemodelan dan sintesis untuk FPGA, Windows belum berakar dalam industri desain chip massal. Pada awal 1990-an, pasar workstation untuk pengembang ASIC terpecah antara SunOS dan HP / UX. Kemudian perusahaan elektronik bermain selama tiga tahun dengan Windows NT, tetapi tidak berhasil. Setelah itu, Synopsys dan perusahaan perangkat lunak desain lainnya meludah dan beralih ke Linux - pertama di Red Hat, kemudian di SuSE dan Ubuntu. Saya curiga, terutama karena banyak skrip pada mutiara, C-shell, dll, serta karena pekerjaan jarak jauh pengembang melalui telnet dan X Window.Oleh karena itu, untuk seminar saya, saya pergi dengan sekelompok SSD bootable dengan Lubuntu, di mana semua perangkat lunak yang diperlukan diinstal. Saya menggunakan boot lama, tetapi baru-baru ini ternyata semakin banyak komputer yang membutuhkan boot UEFI. Rupanya, Anda harus membuat SSD yang dapat di-boot dengan UEFI boot.Perusahaan yang bergerak cepat menggunakan CentOS, bukan Red Hat. Mungkin banyak alat desain dibuat di bawah Debian, tapi saya belum mengujinya.

Di sini Anda mungkin memiliki pertanyaan: mengapa saya menggunakan seminar Linux? Meskipun Windows juga memiliki lingkungan pemodelan dan sintesis untuk FPGA, Windows belum berakar dalam industri desain chip massal. Pada awal 1990-an, pasar workstation untuk pengembang ASIC terpecah antara SunOS dan HP / UX. Kemudian perusahaan elektronik bermain selama tiga tahun dengan Windows NT, tetapi tidak berhasil. Setelah itu, Synopsys dan perusahaan perangkat lunak desain lainnya meludah dan beralih ke Linux - pertama di Red Hat, kemudian di SuSE dan Ubuntu. Saya curiga, terutama karena banyak skrip pada mutiara, C-shell, dll, serta karena pekerjaan jarak jauh pengembang melalui telnet dan X Window.Oleh karena itu, untuk seminar saya, saya pergi dengan sekelompok SSD bootable dengan Lubuntu, di mana semua perangkat lunak yang diperlukan diinstal. Saya menggunakan boot lama, tetapi baru-baru ini ternyata semakin banyak komputer yang membutuhkan boot UEFI. Rupanya, Anda harus membuat SSD yang dapat di-boot dengan UEFI boot.Perusahaan yang bergerak cepat menggunakan CentOS, bukan Red Hat. Mungkin banyak alat desain dibuat di bawah Debian, tapi saya belum mengujinya. Untuk seminar, saya menggunakan papan FPGA Tiongkok, salah satunya dipegang oleh seorang gadis Novosibirsk, Natasha, yang menjadi tuan rumah pesta What-Where-When di Lembah Silikon kami .

Untuk seminar, saya menggunakan papan FPGA Tiongkok, salah satunya dipegang oleh seorang gadis Novosibirsk, Natasha, yang menjadi tuan rumah pesta What-Where-When di Lembah Silikon kami . Pada bulan Maret, saya berjalan melalui satwa liar California bersama dengan pengusaha Rusia Sergei Zorin, yang membawa selusin papan ZEOWAA ke Moskow, dengan karakteristik yang mirip dengan yang dipegang Natasha di tangan mereka.Karena mungkin tidak akan ada seminar di Zelenograd karena coronavirus musim panas ini, saya pikir saya akan memberikan selusin biaya ini kepada anak sekolah Moskow secara gratis (UPD: anak sekolah dari kota lain juga bisa, walaupun ada keributan tambahan dengan penerusan). Dengan dua kondisi:

Pada bulan Maret, saya berjalan melalui satwa liar California bersama dengan pengusaha Rusia Sergei Zorin, yang membawa selusin papan ZEOWAA ke Moskow, dengan karakteristik yang mirip dengan yang dipegang Natasha di tangan mereka.Karena mungkin tidak akan ada seminar di Zelenograd karena coronavirus musim panas ini, saya pikir saya akan memberikan selusin biaya ini kepada anak sekolah Moskow secara gratis (UPD: anak sekolah dari kota lain juga bisa, walaupun ada keributan tambahan dengan penerusan). Dengan dua kondisi:Sebelum Anda mendapatkan papan, Anda harus melalui ketiga bagian dari kursus online "Bagaimana cara kerja pembuat nanochip pintar" ( "Dari transistor ke sirkuit mikro" , "Sisi logis sirkuit digital" , "Sisi fisik sirkuit digital" ), dan mendapatkan sertifikat. Kami menciptakan kursus ini bersama-sama dengan RUSNANO, atau lebih tepatnya, anak perempuan pendidiknya eNano, proyek STEMford.

, , , . , , , ( ) . , , .

, , .

Jika Anda ingin membeli buku baru "Sintesis Logikal " sebagai bantuan untuk proyek semacam itu , maka bagi pembaca Habr ia memiliki kode promosi - Sintez_2020. Di masa depan, alangkah baiknya jika menggunakan papan bahasa Mandarin dan membuat papan Rusia murah untuk latihan semacam itu dengan FPGA, dengan desain terbuka. Saya menyambut jika Anda membagikan pemikiran Anda dalam komentar pada perangkat lunak desain papan dan ide-ide tentang bagaimana merancang dan memasarkan papan tersebut dengan lebih baik. Untuk penggunaan massal dengan anak-anak sekolah, diharapkan harganya tidak lebih dari $ 30 atau 2000 rubel.

Di masa depan, alangkah baiknya jika menggunakan papan bahasa Mandarin dan membuat papan Rusia murah untuk latihan semacam itu dengan FPGA, dengan desain terbuka. Saya menyambut jika Anda membagikan pemikiran Anda dalam komentar pada perangkat lunak desain papan dan ide-ide tentang bagaimana merancang dan memasarkan papan tersebut dengan lebih baik. Untuk penggunaan massal dengan anak-anak sekolah, diharapkan harganya tidak lebih dari $ 30 atau 2000 rubel. Jika Anda seorang mahasiswa dan tertarik dalam desain sirkuit mikro, Anda dapat mengunjungi MIET, HSE MIEM, Institut Fisika Teknik Moskwa, Universitas Negeri Moskow, Institut Fisika dan Teknologi Moskwa ( Nikita Polyakov terlibat dalam latihan semacam itu, MPEI, MISiS, ITMO, LETI, Samara University, beberapa universitas Ukraina (KNU, Chernihiv NTU, Kharkov KNURE) dan universitas lainnya. Jadi saya menemukan bagaimana pendekatan saya kepada komite seleksi MIET di Zelenograd sedang diperbaiki:

Jika Anda seorang mahasiswa dan tertarik dalam desain sirkuit mikro, Anda dapat mengunjungi MIET, HSE MIEM, Institut Fisika Teknik Moskwa, Universitas Negeri Moskow, Institut Fisika dan Teknologi Moskwa ( Nikita Polyakov terlibat dalam latihan semacam itu, MPEI, MISiS, ITMO, LETI, Samara University, beberapa universitas Ukraina (KNU, Chernihiv NTU, Kharkov KNURE) dan universitas lainnya. Jadi saya menemukan bagaimana pendekatan saya kepada komite seleksi MIET di Zelenograd sedang diperbaiki: Tapi di sini adalah bagaimana MIET melihat ke dalam: Anda dapat

Tapi di sini adalah bagaimana MIET melihat ke dalam: Anda dapat menemukan pekerjaan di sana tepat di seberang MIET dengan LSM ELVIS, yang berurusan dengan kamera pintar dan chip satelit:

menemukan pekerjaan di sana tepat di seberang MIET dengan LSM ELVIS, yang berurusan dengan kamera pintar dan chip satelit: Atau Anda bisa datang ke Lembah Silikon. Ingin mendapatkan wawancara dengan Dolina? Berlatih di papan FPGA!

Atau Anda bisa datang ke Lembah Silikon. Ingin mendapatkan wawancara dengan Dolina? Berlatih di papan FPGA!