शायद यह सवाल "यह कैसे काम करता है" बहुतों को मूर्खतापूर्ण लगता है। उत्तर लगभग स्पष्ट है: एक पता करने योग्य एलईडी पट्टी में श्रृंखला में जुड़े "स्मार्ट एलईडी" की बहुलता है। यह टेप डिवाइस को देखकर बस देखा जा सकता है। आप एक लचीली केबल के लिए अलग-अलग माइक्रोक्रिस्किट्स देख सकते हैं, आप कनेक्शन देख सकते हैं: माइक्रोक्रिस्केट्स केवल तीन तारों के साथ श्रृंखला में जुड़े हुए हैं, और उनमें से दो पावर और ग्राउंड हैं। केवल एक तार पिक्सेल रंग डेटा प्रसारित करता है। यह कैसा है? स्मार्ट एलईडी क्या है?इसके बाद, मैं WS2812B- आधारित एलईडी पट्टी में उपयोग किए जाने वाले डेटा ट्रांसफर प्रोटोकॉल के बारे में बात करूंगा, और, इसके अलावा, मैं लगभग FPGA चिप में अपनी खुद की "एलईडी स्ट्रिप चिप" बनाऊंगा।इसलिए, टेप एकल डेटा सिग्नल के माध्यम से सीरियल ट्रांसमिशन का उपयोग करता है।बिट शून्य को एक सकारात्मक धनात्मक आवेग के रूप में प्रेषित किया जाता है और एक आवेग जो आवेग की तुलना में लगभग दो गुना व्यापक है। बिट यूनिट को एक विस्तृत पॉजिटिव पल्स और एक शॉर्ट पॉज़ के रूप में प्रेषित किया जाता है:

शायद यह सवाल "यह कैसे काम करता है" बहुतों को मूर्खतापूर्ण लगता है। उत्तर लगभग स्पष्ट है: एक पता करने योग्य एलईडी पट्टी में श्रृंखला में जुड़े "स्मार्ट एलईडी" की बहुलता है। यह टेप डिवाइस को देखकर बस देखा जा सकता है। आप एक लचीली केबल के लिए अलग-अलग माइक्रोक्रिस्किट्स देख सकते हैं, आप कनेक्शन देख सकते हैं: माइक्रोक्रिस्केट्स केवल तीन तारों के साथ श्रृंखला में जुड़े हुए हैं, और उनमें से दो पावर और ग्राउंड हैं। केवल एक तार पिक्सेल रंग डेटा प्रसारित करता है। यह कैसा है? स्मार्ट एलईडी क्या है?इसके बाद, मैं WS2812B- आधारित एलईडी पट्टी में उपयोग किए जाने वाले डेटा ट्रांसफर प्रोटोकॉल के बारे में बात करूंगा, और, इसके अलावा, मैं लगभग FPGA चिप में अपनी खुद की "एलईडी स्ट्रिप चिप" बनाऊंगा।इसलिए, टेप एकल डेटा सिग्नल के माध्यम से सीरियल ट्रांसमिशन का उपयोग करता है।बिट शून्य को एक सकारात्मक धनात्मक आवेग के रूप में प्रेषित किया जाता है और एक आवेग जो आवेग की तुलना में लगभग दो गुना व्यापक है। बिट यूनिट को एक विस्तृत पॉजिटिव पल्स और एक शॉर्ट पॉज़ के रूप में प्रेषित किया जाता है: यदि 50 से अधिक माइक्रोसेकंड का कोई प्रसारण नहीं है, तो टेप अपने मूल राज्य में वापस चला जाता है, पहले से शुरू होने वाले पिक्सल को स्वीकार करने के लिए तैयार है।एक अनुक्रम में प्रत्येक 24 बिट्स तीन आरजीबी रंगों के लिए 3 बाइट्स हैं। और वास्तव में अनुक्रम जीआरबी होगा। जी 7 का उच्च बिट पहले आता है।पहले 24 बिट्स का अनुक्रम एक पिक्सेल है, जो टेप में बहुत पहले एलईडी प्राप्त करेगा। जब तक पहली एलईडी संतृप्त नहीं होती है, तब तक यह डेटा को अगली एलईडी पर स्थानांतरित नहीं करता है। पहला एलईडी 24x आरजीबी बिट्स के अपने हिस्से को प्राप्त करने के बाद, यह ट्रांसमिशन को अगले पर खोलता है। मुख्य रूप से, एक एल ई डी के अनुक्रम की कल्पना कर सकता है कि उत्तराधिकार में पानी से भरे हुए गुड़ के एक झरने के रूप में:

यदि 50 से अधिक माइक्रोसेकंड का कोई प्रसारण नहीं है, तो टेप अपने मूल राज्य में वापस चला जाता है, पहले से शुरू होने वाले पिक्सल को स्वीकार करने के लिए तैयार है।एक अनुक्रम में प्रत्येक 24 बिट्स तीन आरजीबी रंगों के लिए 3 बाइट्स हैं। और वास्तव में अनुक्रम जीआरबी होगा। जी 7 का उच्च बिट पहले आता है।पहले 24 बिट्स का अनुक्रम एक पिक्सेल है, जो टेप में बहुत पहले एलईडी प्राप्त करेगा। जब तक पहली एलईडी संतृप्त नहीं होती है, तब तक यह डेटा को अगली एलईडी पर स्थानांतरित नहीं करता है। पहला एलईडी 24x आरजीबी बिट्स के अपने हिस्से को प्राप्त करने के बाद, यह ट्रांसमिशन को अगले पर खोलता है। मुख्य रूप से, एक एल ई डी के अनुक्रम की कल्पना कर सकता है कि उत्तराधिकार में पानी से भरे हुए गुड़ के एक झरने के रूप में: पहला, फिर दूसरा, फिर तीसरा, और इसी तरह , बारी-बारी से भरा जाएगा ।इस प्रकार, मेरा मानना है कि स्थानांतरण प्रोटोकॉल को सुलझा लिया गया है।क्या इस तरह के "स्मार्ट एलईडी" को स्वयं डिजाइन करने का प्रयास करना संभव है? बेशक, यह थोड़ा व्यावहारिक अर्थ रखता है, लेकिन आत्म-शिक्षा और किसी के क्षितिज को व्यापक बनाने के लिए, यह एक दिलचस्प काम है। आइए प्रोग्रामिंग भाषा वेरिलॉग एचडीएल में चिप के तर्क का वर्णन करने का प्रयास करें। बेशक, यह एक वास्तविक चिप डिजाइन नहीं होगा, सीमाएं होंगी। सबसे महत्वपूर्ण सीमाओं में से एक - मुझे अपने माइक्रोकिरसीट के लिए एक बाहरी घड़ी की आवश्यकता होगी। एक असली स्मार्ट एलईडी में, ऐसा जनरेटर भी मौजूद है, लेकिन यह पहले से ही चिप में एकीकृत है।इस तरह Verilog मॉड्यूल शुरू करते हैं:

पहला, फिर दूसरा, फिर तीसरा, और इसी तरह , बारी-बारी से भरा जाएगा ।इस प्रकार, मेरा मानना है कि स्थानांतरण प्रोटोकॉल को सुलझा लिया गया है।क्या इस तरह के "स्मार्ट एलईडी" को स्वयं डिजाइन करने का प्रयास करना संभव है? बेशक, यह थोड़ा व्यावहारिक अर्थ रखता है, लेकिन आत्म-शिक्षा और किसी के क्षितिज को व्यापक बनाने के लिए, यह एक दिलचस्प काम है। आइए प्रोग्रामिंग भाषा वेरिलॉग एचडीएल में चिप के तर्क का वर्णन करने का प्रयास करें। बेशक, यह एक वास्तविक चिप डिजाइन नहीं होगा, सीमाएं होंगी। सबसे महत्वपूर्ण सीमाओं में से एक - मुझे अपने माइक्रोकिरसीट के लिए एक बाहरी घड़ी की आवश्यकता होगी। एक असली स्मार्ट एलईडी में, ऐसा जनरेटर भी मौजूद है, लेकिन यह पहले से ही चिप में एकीकृत है।इस तरह Verilog मॉड्यूल शुरू करते हैं:module WS2812B(

input wire clk,

input wire in,

output wire out,

output reg r,

output reg g,

output reg b

);

मुझे लगता है कि यहां सब कुछ स्पष्ट है: क्लॉक की क्लॉक फ़्रीक्वेंसी, इन-आउट और आउट, और निश्चित रूप से, आउटपुट सिग्नल r, g, b की इनपुट आवृत्ति और आउटपुट सिग्नल, जिसके माध्यम से मैं लाल, हरे और नीले रंग में वास्तविक बाहरी एल ई डी को नियंत्रित करूंगा।मैं दो-बिट शिफ्ट रजिस्टर में इनपुट सिग्नल कैप्चर करूंगा और इन कैप्चर किए गए बिट्स में वर्तमान स्थिति से मैं सिग्नल के पॉजिटिव एज की शुरुआत निर्धारित कर सकता हूं:reg [1:0]r_in = 0;

always @( posedge clk )

r_in <= { r_in[0],in };

wire in_pos_edge; assign in_pos_edge = (r_in==2'b01);

इसके अलावा, एक नया ट्रांसमिशन शुरू करने से पहले कंट्रोल कंट्रोलर के रुकने पर टेप रीसेट की स्थिति निर्धारित करना महत्वपूर्ण है:localparam reset_level = 3000;

reg [15:0]reset_counter = 0;

always @( posedge clk )

if( r_in[0] )

reset_counter <= 0;

else

if( reset_counter<reset_level )

reset_counter <= reset_counter+1;

wire reset; assign reset = (reset_counter==reset_level);

इसके अलावा, एक सकारात्मक बढ़त से in_pos_edge के लिए कुछ ठहराव का सामना करने के लिए आवश्यक है ताकि एक नया समय तय करने के क्षण को प्राप्त किया जा सके:localparam fix_level = 50;

reg [7:0]bit_length_cnt;

always @( posedge clk )

if( in_pos_edge )

bit_length_cnt <= 0;

else

if( bit_length_cnt<(fix_level+1) && !pass )

bit_length_cnt <= bit_length_cnt + 1;

wire bit_fix; assign bit_fix = (bit_length_cnt==fix_level);

चिप में पहले से ही प्राप्त बिट्स की संख्या निम्नानुसार मानी जाती है:reg pass = 0;

reg [5:0]bits_captured = 0;

always @( posedge clk )

if( reset )

bits_captured <= 1'b0;

else

if( ~pass && bit_fix )

bits_captured <= bits_captured+1'b1;

यहां एक महत्वपूर्ण पास सिग्नल पेश किया गया है, जो आउटपुट पर इनपुट स्ट्रीम के पुनर्निर्देशन को निर्धारित करता है। 24x पिक्सेल बिट स्वीकार करने के बाद, पास सिग्नल एक पर सेट होता है:always @( posedge clk )

if( reset )

pass <= 1'b0;

else

if( bits_captured==23 && bit_fix )

pass <= 1'b1;

reg pass_final;

always @( posedge clk )

if( reset )

pass_final <= 1'b0;

else

if( r_in!=2'b11 )

pass_final <= pass;

assign out = pass_final ? in : 1'b0;

जब पास_फाइनल सिग्नल एक होता है तो इनपुट आउट को आउटपुट से गुणा किया जाता है।ठीक है, निश्चित रूप से, हमें एक शिफ्ट रजिस्टर की आवश्यकता है, जहां पिक्सेल के 24 बिट्स संचित हैं:reg [23:0]shift_rgb;

always @( posedge clk )

if( bit_fix )

shift_rgb <= { in, shift_rgb[23:1] };

reg [23:0]fix_rgb;

always @( posedge clk )

if( bits_captured==23 && bit_fix )

fix_rgb <= { in, shift_rgb[23:1] };

सभी 24 बिट्स प्राप्त होने पर, उन्हें अंतिम 24 बिट रजिस्टर के लिए भी कॉपी किया जाता है।अब मामला छोटा रह गया है। प्राप्त RGB बाइट्स के अनुसार वास्तविक बाहरी एल ई डी में चमक को संचारित करने के लिए PWM (लैटिट्यूडिनल पल्स मॉड्यूलेशन) सिग्नल को लागू करना आवश्यक है:wire [7:0]wgreen; assign wgreen = { fix_rgb[0 ], fix_rgb[1 ], fix_rgb[2 ], fix_rgb[3 ], fix_rgb[4 ], fix_rgb[5 ], fix_rgb[6 ], fix_rgb[7 ] };

wire [7:0]wred; assign wred = { fix_rgb[8 ], fix_rgb[9 ], fix_rgb[10], fix_rgb[11], fix_rgb[12], fix_rgb[13], fix_rgb[14], fix_rgb[15] };

wire [7:0]wblue; assign wblue = { fix_rgb[16], fix_rgb[17], fix_rgb[18], fix_rgb[19], fix_rgb[20], fix_rgb[21], fix_rgb[22], fix_rgb[23] };

reg [7:0]pwm_cnt;

always @( posedge clk )

begin

pwm_cnt <= pwm_cnt+1;

r <= pwm_cnt<wred;

g <= pwm_cnt<wgreen;

b <= pwm_cnt<wblue;

end

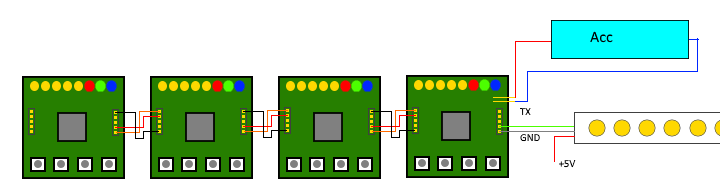

वह सब मालूम होता है।एक छोटा सा विवरण है - यह सब कैसे अनुभव किया जाए?मैंने FPGA MAX II (ये मार्स रोवर सीरीज़ कार्ड हैं) के साथ कुछ सरल मदरबोर्ड लिए और इस वेरिलॉग कोड के साथ प्रोजेक्ट के साथ उन सभी को फ्लैश किया। बोर्डों पर पहले से ही 8 एलईडी थे, लेकिन वे सभी पीले थे। प्रत्येक बोर्ड पर, मैंने 3 एलईडी को आर, जी, बी से बदल दिया। मैंने बोर्ड को श्रृंखला में जोड़ा और, इसके अलावा, उन्हें एक वास्तविक एलईडी पट्टी से जोड़ा। इस प्रकार, मैंने अपने होममेड एल ई डी के साथ वास्तविक टेप को लंबा कर दिया।यह कनेक्शन इस तरह से निकला: वास्तव में, यह इस तरह दिखता है:

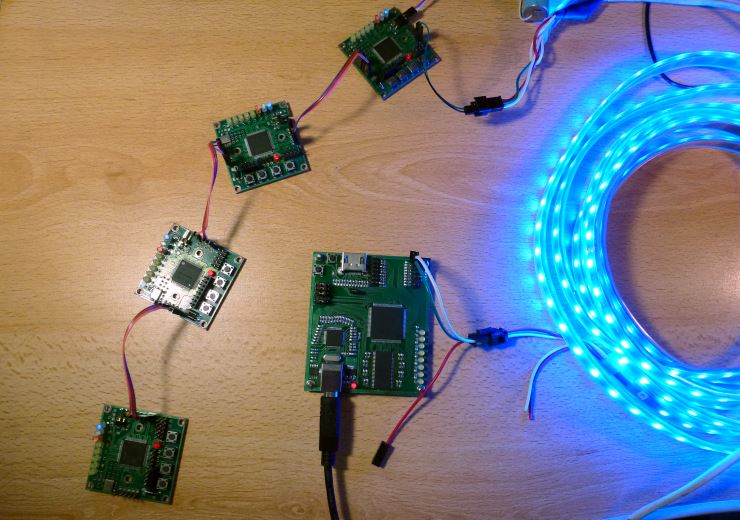

वास्तव में, यह इस तरह दिखता है: अब, टेप में एक निश्चित छवि को लागू करते हुए, मैं देखता हूं कि मेरे "स्मार्ट एलईडी" टेप से वास्तविक लोगों की तरह व्यवहार करते हैं:यह पता चला है कि FPGA में मैंने जो तर्क लागू किया है वह पूरी तरह कार्यात्मक है! पहले सन्निकटन के रूप में, मैं एक वास्तविक स्मार्ट एलईडी चिप के समान कुछ करने में सक्षम था।दरअसल, मुझे एलईडी स्ट्रिप्स पसंद हैं। उनके आधार पर, हर कोई अपना खुद का कुछ आविष्कार कर सकता है: बुद्धिमान प्रकाश, स्क्रीन, अस्पष्ट प्रभाव। एक बार मैंने FPGA पर चलने वाले एक एलईडी टेप पर रंगीन संगीत भी लागू किया। लेकिन वह एक और कहानी है ।

अब, टेप में एक निश्चित छवि को लागू करते हुए, मैं देखता हूं कि मेरे "स्मार्ट एलईडी" टेप से वास्तविक लोगों की तरह व्यवहार करते हैं:यह पता चला है कि FPGA में मैंने जो तर्क लागू किया है वह पूरी तरह कार्यात्मक है! पहले सन्निकटन के रूप में, मैं एक वास्तविक स्मार्ट एलईडी चिप के समान कुछ करने में सक्षम था।दरअसल, मुझे एलईडी स्ट्रिप्स पसंद हैं। उनके आधार पर, हर कोई अपना खुद का कुछ आविष्कार कर सकता है: बुद्धिमान प्रकाश, स्क्रीन, अस्पष्ट प्रभाव। एक बार मैंने FPGA पर चलने वाले एक एलईडी टेप पर रंगीन संगीत भी लागू किया। लेकिन वह एक और कहानी है ।