नमस्कार, हेब्र!

अब कई वर्षों से, मैं सी + + में stm32 माइक्रोकंट्रोलर लाइन के लिए अपनी सभी परियोजनाएं कर रहा हूं।

इस समय के दौरान, मैंने एक निश्चित मात्रा में सामग्री जमा की है जो अन्य डेवलपर्स के लिए ब्याज की हो सकती है।

अनावश्यक प्रश्नों से बचने के लिए: मैं QtCreator + gcc + gdb + openocd का एक गुच्छा उपयोग करता हूं। इसके साथ काम करने के बारे में कई बार बताया गया है, इसलिए मैं वहाँ नहीं रुकता, लेकिन मैं आपको माइक्रोकंट्रोलर के साथ काम करने के बारे में अपने दृष्टिकोण के बारे में अधिक बताता हूँ।

परियोजना के निचले स्तर पर, एक नियम के रूप में, परिधीय चालक हैं। चलो उनके साथ शुरू करते हैं।

मैं कोशिश करता हूं, यदि संभव हो, तो एसपीएल, एचएएल और भगवान जैसे राक्षसों के साथ खिलवाड़ न करें, भगवान मुझे माफ करें, क्यूबमैक्स, पैसे के लिए अन्य लोगों की परियोजनाओं को खत्म करने के अलावा। मेरी राय में, "बड़ी मशीनों के लिए" रूपरेखा की विचारधारा, वहाँ शातिर है। लचीले और उपयोग में आसान होने के कारण (हालांकि कोई इसके साथ बहस करेगा) फ़ंक्शन एक बड़े और उप-रूपी मशीन कोड में बदल जाते हैं, जहां रनटाइम में माइक्रोकंट्रोलर पर कई अनावश्यक ऑपरेशन किए जाते हैं। हां, आधुनिक नियंत्रक शक्तिशाली हैं, लेकिन जिस कंप्यूटर पर हम परियोजना को इकट्ठा करते हैं, वह अधिक शक्तिशाली है, इसलिए इसे सब कुछ करने दें।

मैंने अपने लिए परिधीय प्रबंधन के कार्यान्वयन के लिए बुनियादी आवश्यकताओं को निर्धारित किया:

- सभी निरंतर अभिव्यक्तियों को संकलन चरण में गणना की जानी चाहिए और संख्याओं के रूप में मशीन कोड में गिरना चाहिए;

- संकलक को कार्य के शेर की हिस्सेदारी करनी चाहिए, साथ ही कार्यों को दिए गए प्रकारों को नियंत्रित करना चाहिए;

- मैक्रो

जरूरत नहीं कम से कम इस्तेमाल किया जाना चाहिए, जहां यह प्रकार के नियंत्रण को कमजोर करने के लिए नेतृत्व नहीं करता है; - कार्यान्वयन प्रोग्रामिंग इंटरफ़ेस को कोड पठनीयता का समर्थन करना चाहिए।

संभवतः केवल आलसी ने रजिस्टर फ़ील्ड के साथ काम करने के लिए अपनी बाइक का आविष्कार नहीं किया। यह एक शिफ्ट प्लस लॉजिकल ऑपरेशंस एक ला सीएमएसआईएस है, और मैक्रोज़ के सभी प्रकार जो अपने जटिल आंत्रों में समान संचालन को छिपाते हैं और एसटी से पुस्तकालयों की शैली में हैं। एक समय पर, मैंने भी बिट फ़ील्ड के माध्यम से काम किया, आखिरकार, मैं एक समाधान के साथ आया, जिसके साथ मैं आपका परिचय करना चाहता हूं।

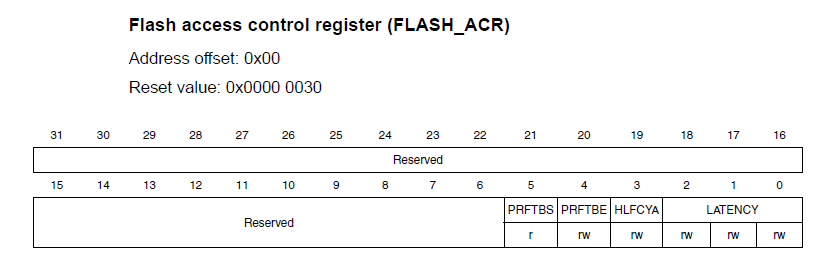

इसके बाद, एक उदाहरण के रूप में, मैं चीनी एसटीएम 32 एफ 103 और उसके फ्लैश एक्सेस कंट्रोल रजिस्टर द्वारा बहुत प्यारे का उपयोग करूंगा, जो कि वहां है, इसलिए उदाहरण सरल और छोटा होगा।

flash CMSIS 72:

FLASH->ACR = (FLASH->ACR &

(~(FLASH_ACR_LATENCY_Msk

| FLASH_ACR_PRFTBE_Msk )))

| FLASH_ACR_LATENCY_1

| FLASH_ACR_PRFTBE;

, ? , - , , . . , , :

0x80001ec 04 4a ldr r2, [pc, #16] ; (0x8000200 <main()+20>)

0x80001ee <+ 2> 13 68 ldr r3, [r2, #0]

0x80001f0 <+ 4> 23 f0 17 03 bic.w r3, r3, #23

0x80001f4 <+ 8> 43 f0 12 03 orr.w r3, r3, #18

0x80001f8 <+ 12> 13 60 str r3, [r2, #0]

, : --. ?

. .

, . . flash :

struct Regs {

uint32_t ACR;

};

:

struct ACR {

constexpr static uint8_t LATENCY[]{ 0, 3 };

constexpr static uint8_t HLFCYA[]{ 3, 1 };

constexpr static uint8_t PRFTBE[]{ 4, 1 };

constexpr static uint8_t PRFTBS[]{ 5, 1 };

};

— , — . Python SVD .

, . constexpr :

constexpr static uint32_t base = 0x40022000;

INLINE constexpr static volatile Regs* rg()

{

return reinterpret_cast<volatile Regs*>(base);

}

base , (, , , , ) . .

INLINE

#ifndef INLINE

#define INLINE __attribute__((__always_inline__)) inline

#endif

, . , , gcc .

flash :

INLINE static void setLatency(Flash::Latency latency, bool prefetchBufferEnable = false)

{

setRegister(rg()->ACR,

ACR::LATENCY, static_cast<uint8_t>(latency),

ACR::PRFTBE, prefetchBufferEnable

);

}

, : , . latency , . static_cast<uint8_t>(latency) , , , Latency :

enum class Latency : uint8_t {

zeroWaitState = 0b000,

oneWaitState = 0b001,

twoWaitStates = 0b010

};

Flash::setLatency(Flash::Latency::twoWaitStates, true);

:

0x80001ec 04 4a ldr r2, [pc, #16] ; (0x8000200 <main()+20>)

0x80001ee <+ 2> 13 68 ldr r3, [r2, #0]

0x80001f0 <+ 4> 23 f0 17 03 bic.w r3, r3, #23

0x80001f4 <+ 8> 43 f0 12 03 orr.w r3, r3, #18

0x80001f8 <+ 12> 13 60 str r3, [r2, #0]

CMSIS: --, .

? setRegister. :

template<typename T, typename V, typename... Args>

INLINE constexpr static void setRegister(volatile uint32_t& reg,

const T field,

const V value,

const Args... args)

{

uint32_t mask = setMaskR(field, value, args...);

uint32_t val = setBitsR(field, value, args...);

reg = (reg & (~mask)) | val;

}

( uint32_t) — . .

:

template<typename V, typename T>

INLINE constexpr static uint32_t setBitsR(T field, V val)

{

return (val << (field[0]));

}

template<typename V, typename T, typename... Args>

INLINE constexpr static uint32_t setBitsR(T field, V val, Args... args)

{

return (val << (field[0])) | setBitsR(args...);

}

template<typename V, typename T>

INLINE constexpr static uint32_t setMaskR(T field, V val)

{

return ((((1 << field[1]) - 1) << field[0]));

}

template<typename V, typename T, typename... Args>

INLINE constexpr static uint32_t setMaskR(T field, V val, Args... args)

{

return ((((1 << field[1]) - 1) << field[0])) | setMaskR(args...);

}

"" . " " , , , , , , .

setRegister? . , - - — . , , , , volatile, , . , , .

. :

Flash::setLatency(Flash::Latency::twoWaitStates, true);

Flash::setLatency(Flash::Latency::oneWaitState, true);

--:

0x80001ec 07 4a ldr r2, [pc, #28] ; (0x800020c <main()+32>)

0x80001ee <+ 2> 13 68 ldr r3, [r2, #0]

0x80001f0 <+ 4> 23 f0 17 03 bic.w r3, r3, #23

0x80001f4 <+ 8> 43 f0 12 03 orr.w r3, r3, #18

0x80001f8 <+ 12> 13 60 str r3, [r2, #0] ;

0x80001fa <+ 14> 13 68 ldr r3, [r2, #0]

0x80001fc <+ 16> 23 f0 17 03 bic.w r3, r3, #23

0x8000200 <+ 20> 43 f0 11 03 orr.w r3, r3, #17

0x8000204 <+ 24> 13 60 str r3, [r2, #0] ;

:

template<typename T>

INLINE constexpr static uint32_t getRegField(volatile uint32_t& reg,

const T field)

{

uint32_t mask = (((1 << field[1]) - 1) << field[0]);

return ((reg & mask) >> field[0]);

}

.

— :

INLINE static bool getLatencyPrefetch()

{

return getRegField(rg()->ACR,

ACR::LATENCY,

ACR::PRFTBE);

}

flash :

struct Flash {

constexpr static uint32_t base = 0x40022000;

struct ACR {

constexpr static uint8_t LATENCY[]{ 0, 3 };

constexpr static uint8_t HLFCYA[]{ 3, 1 };

constexpr static uint8_t PRFTBE[]{ 4, 1 };

constexpr static uint8_t PRFTBS[]{ 5, 1 };

};

enum class Latency : uint8_t {

zeroWaitState = 0b000,

oneWaitState = 0b001,

twoWaitStates = 0b010

};

INLINE constexpr static volatile Regs* rg()

{

return reinterpret_cast<volatile Regs*>(base);

}

INLINE static void setLatency(Flash::Latency latency, bool prefetchBufferEnable = false)

{

Utility::setRegister(rg()->ACR,

ACR::LATENCY, static_cast<uint8_t>(latency),

ACR::PRFTBE, prefetchBufferEnable

);

}

INLINE static bool getLatencyPrefetch()

{

return getRegField(rg()->ACR,

ACR::LATENCY,

ACR::PRFTBE);

}

};

. , , . .

- , .

, . , DSP-. — .