Le nouveau laboratoire de synthèse numérique poursuit la tradition du didacticiel de David Harris et Sarah Harris, Circuit numérique et architecture informatique, qui a téléchargé le site britannique . Le laboratoire vous permet de toucher toute la théorie de Harris & Harris sur la carte FPGA, des lumières clignotantes au processeur. Le concept de traitement des convoyeurs est également analysé en laboratoire, sans lequel vous ne passerez pas d'entretien pour travailler en tant que designer dans une entreprise de microélectronique. À la fin, le chemin du FPGA à l'ASIC, des circuits de masse qui se trouvent dans les accélérateurs iPhones, Tesla et AI.Le livre contient une interview d'une équipe de Saint-Pétersbourg qu'Intel a apportée à son siège social de la Silicon Valley pour sa victoire au concours Innovate FPGA. Livre "Synthèse numérique: un cours pratique"Cadence Design Systems, une entreprise leader dans l'automatisation de la conception de microcircuits, a pris en charge (sur la photo ci-dessus, Sibérie Natasha est debout avec une carte FPGA devant le siège de Cadence dans la Silicon Valley - sa vidéo sera dans le post).Labnik a été créé sous les auspices de l' École supérieure d'économie / MIEM (Alexander Romanov, Veronika Prokhorova et Igor Agamirzyan), tandis que différents chapitres ont été rédigés par des enseignants des universités de Moscou, Kiev et Samara, de l'ITMO de Saint-Pétersbourg, de l'École polytechnique de Tchernihiv et de l'Université de Californie à Santa Cruz ( Charles Danchek , bureau du soir dans la Silicon Valley). La création du manuel a été suivie par les ingénieurs de la société russe IVA Technologies (Stanislav Zhelnio, accélérateur matériel AI + projet éducatif schoolMIPS) et FSUE NPTSAP(département de Roscosmos), les sociétés américaines MIPS, Juniper Networks et AMD. Publié un manuel DMK-Press.J'ai élaboré un plan pour le laboratoire et attiré des auteurs de projets éducatifs précédents, après quoi j'ai transféré le contrôle à Alexander Romanov, qui a effectué un travail minutieux, gérant le projet pendant près de deux ans. La création du manuel s'inscrit naturellement dans les activités d'Alexandre , qui a élevé pendant 3 ans le laboratoire du HSE MIEM , qui s'occupe des ordinateurs embarqués, de la robotique et des FPGA. Le laboratoire a organisé plusieurs équipes à l'Innovate FPGA, dont l' une est devenue médaillée de bronze en finale régionale.Le manuel ne convient pas seulement aux étudiants - il peut être utilisé pour les camps d'été de conception numérique pour les étudiants avancés. Comprendre les didacticiels sur Internet à partir de zéro sur la façon de travailler avec l'environnement Intel Quartus II n'est pas anodin. Et dans le manuel, tout est décrit par étapes. De plus, il a toutes les bases théoriques pour faire quelque chose d'intéressant pour les écoliers, en plus des lumières clignotantes qui les dérangent rapidement. Intéressant est par exemple un jeu vidéo:

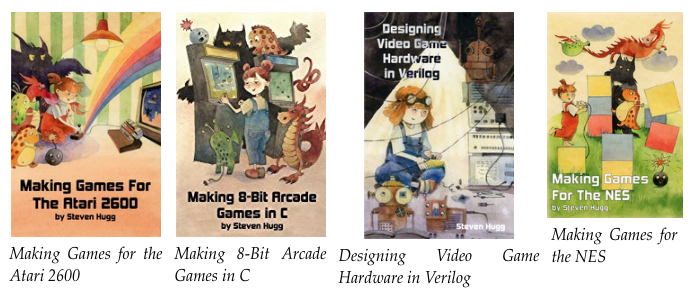

Le nouveau laboratoire de synthèse numérique poursuit la tradition du didacticiel de David Harris et Sarah Harris, Circuit numérique et architecture informatique, qui a téléchargé le site britannique . Le laboratoire vous permet de toucher toute la théorie de Harris & Harris sur la carte FPGA, des lumières clignotantes au processeur. Le concept de traitement des convoyeurs est également analysé en laboratoire, sans lequel vous ne passerez pas d'entretien pour travailler en tant que designer dans une entreprise de microélectronique. À la fin, le chemin du FPGA à l'ASIC, des circuits de masse qui se trouvent dans les accélérateurs iPhones, Tesla et AI.Le livre contient une interview d'une équipe de Saint-Pétersbourg qu'Intel a apportée à son siège social de la Silicon Valley pour sa victoire au concours Innovate FPGA. Livre "Synthèse numérique: un cours pratique"Cadence Design Systems, une entreprise leader dans l'automatisation de la conception de microcircuits, a pris en charge (sur la photo ci-dessus, Sibérie Natasha est debout avec une carte FPGA devant le siège de Cadence dans la Silicon Valley - sa vidéo sera dans le post).Labnik a été créé sous les auspices de l' École supérieure d'économie / MIEM (Alexander Romanov, Veronika Prokhorova et Igor Agamirzyan), tandis que différents chapitres ont été rédigés par des enseignants des universités de Moscou, Kiev et Samara, de l'ITMO de Saint-Pétersbourg, de l'École polytechnique de Tchernihiv et de l'Université de Californie à Santa Cruz ( Charles Danchek , bureau du soir dans la Silicon Valley). La création du manuel a été suivie par les ingénieurs de la société russe IVA Technologies (Stanislav Zhelnio, accélérateur matériel AI + projet éducatif schoolMIPS) et FSUE NPTSAP(département de Roscosmos), les sociétés américaines MIPS, Juniper Networks et AMD. Publié un manuel DMK-Press.J'ai élaboré un plan pour le laboratoire et attiré des auteurs de projets éducatifs précédents, après quoi j'ai transféré le contrôle à Alexander Romanov, qui a effectué un travail minutieux, gérant le projet pendant près de deux ans. La création du manuel s'inscrit naturellement dans les activités d'Alexandre , qui a élevé pendant 3 ans le laboratoire du HSE MIEM , qui s'occupe des ordinateurs embarqués, de la robotique et des FPGA. Le laboratoire a organisé plusieurs équipes à l'Innovate FPGA, dont l' une est devenue médaillée de bronze en finale régionale.Le manuel ne convient pas seulement aux étudiants - il peut être utilisé pour les camps d'été de conception numérique pour les étudiants avancés. Comprendre les didacticiels sur Internet à partir de zéro sur la façon de travailler avec l'environnement Intel Quartus II n'est pas anodin. Et dans le manuel, tout est décrit par étapes. De plus, il a toutes les bases théoriques pour faire quelque chose d'intéressant pour les écoliers, en plus des lumières clignotantes qui les dérangent rapidement. Intéressant est par exemple un jeu vidéo: L'idée d'apprendre verilo via des jeux VGA n'est pas nouvelle - de nombreuses universités ont un tel laboratoire, par exemple au Massachusetts Institute of Technology (MIT) 6.111 Introductory Digital Systems Laboratory. Il y a également deux ans, le livre Designing Video Game Hardware in Verilog Paperback de Steven Hugg a été publié, avec des jeux assez développés avec des chars, des voitures de course, un générateur de ciel étoilé pseudo-aléatoire utilisant LFSR, un tampon de trame et même une interface matériel-logiciel. De plus, les jeux VGA sont en démo des fabricants de FPGA Xilinx et Intel / Altera, plus précisément de leurs sociétés partenaires - Digilent et Terasic.

L'idée d'apprendre verilo via des jeux VGA n'est pas nouvelle - de nombreuses universités ont un tel laboratoire, par exemple au Massachusetts Institute of Technology (MIT) 6.111 Introductory Digital Systems Laboratory. Il y a également deux ans, le livre Designing Video Game Hardware in Verilog Paperback de Steven Hugg a été publié, avec des jeux assez développés avec des chars, des voitures de course, un générateur de ciel étoilé pseudo-aléatoire utilisant LFSR, un tampon de trame et même une interface matériel-logiciel. De plus, les jeux VGA sont en démo des fabricants de FPGA Xilinx et Intel / Altera, plus précisément de leurs sociétés partenaires - Digilent et Terasic. En particulier, dans le laboratoire du MITil est très clairement montré que tout ce que vous devez faire pour dessiner sur l'écran est d'implémenter sous la forme d'un diagramme une fonction qui prend les coordonnées X et Y d'un point sur l'écran comme argument et renvoie la couleur de ce point (RVB). Dans le cas le plus simple, cette fonction est une fonction de combinaison, par exemple, une telle fonction dessinera le chef-d'œuvre de Malevitch: «la couleur est noire (RVB = 0,0,0) si x> = 200 et x <= 400 et y> = 200 et y <400, sinon blanc (RVB = 1,1,1). " Nous appellerons en outre un tel circuit un «mélangeur», car il «mélangera» les entrées de générateurs d'images différentes.Pour générer les arguments du mélangeur X et Y eux-mêmes, un simple circuit à deux compteurs est utilisé qui utilise le signal d'horloge CLK. En plus des coordonnées X et Y, ce circuit génère également des signaux HSYNC et VSYNC pour l'affichage VGA. Les signaux HSYNC et VSYNC sont restés depuis l'époque du tube cathodique. Ils indiquent au faisceau virtuel quand passer horizontalement au point / pixel suivant sur l'écran, puis verticalement à la ligne suivante.Dans un cas difficile, le mélangeur utilise non seulement les valeurs de ses entrées X et Y, mais également les valeurs des éléments d'état (bascules D et mémoire), qui sont enregistrées en utilisant le signal d'horloge CLK. Dans ce cas, l'horloge entre également dans le mélangeur. Les circuits avec des signaux d'horloge et des éléments d'état sont appelés séquentiels (ces circuits passent par une séquence d'états qui pulsent clairement un signal d'horloge pulsé). Sur les mélangeurs série, vous pouvez implémenter des images animées de tout degré de complexité.Voici les images du laboratoire shnaya du MIT (la même chose est dans le tas d'autres universités) illustrant la fonction du générateur HSYNC / VSYNC, le mélangeur (de la même unité qui calcule le RVB en fonction de X / HCOUNT et Y / VCOUNT), ainsi que la sortie de HSYNC, VSYNC et RGB sur l'écran. L'image utilise un commutateur / multiplexeur entre trois mélangeurs - l'un dessine des rayures, un autre dessine un rectangle et le troisième dessine une image à l'écran tout en jouant au ping-pong:

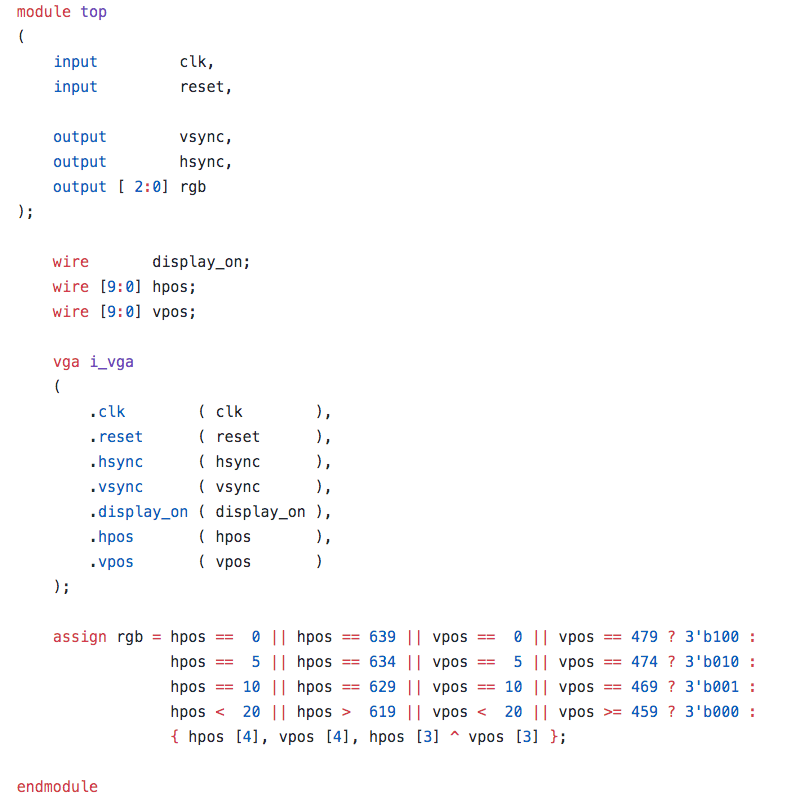

En particulier, dans le laboratoire du MITil est très clairement montré que tout ce que vous devez faire pour dessiner sur l'écran est d'implémenter sous la forme d'un diagramme une fonction qui prend les coordonnées X et Y d'un point sur l'écran comme argument et renvoie la couleur de ce point (RVB). Dans le cas le plus simple, cette fonction est une fonction de combinaison, par exemple, une telle fonction dessinera le chef-d'œuvre de Malevitch: «la couleur est noire (RVB = 0,0,0) si x> = 200 et x <= 400 et y> = 200 et y <400, sinon blanc (RVB = 1,1,1). " Nous appellerons en outre un tel circuit un «mélangeur», car il «mélangera» les entrées de générateurs d'images différentes.Pour générer les arguments du mélangeur X et Y eux-mêmes, un simple circuit à deux compteurs est utilisé qui utilise le signal d'horloge CLK. En plus des coordonnées X et Y, ce circuit génère également des signaux HSYNC et VSYNC pour l'affichage VGA. Les signaux HSYNC et VSYNC sont restés depuis l'époque du tube cathodique. Ils indiquent au faisceau virtuel quand passer horizontalement au point / pixel suivant sur l'écran, puis verticalement à la ligne suivante.Dans un cas difficile, le mélangeur utilise non seulement les valeurs de ses entrées X et Y, mais également les valeurs des éléments d'état (bascules D et mémoire), qui sont enregistrées en utilisant le signal d'horloge CLK. Dans ce cas, l'horloge entre également dans le mélangeur. Les circuits avec des signaux d'horloge et des éléments d'état sont appelés séquentiels (ces circuits passent par une séquence d'états qui pulsent clairement un signal d'horloge pulsé). Sur les mélangeurs série, vous pouvez implémenter des images animées de tout degré de complexité.Voici les images du laboratoire shnaya du MIT (la même chose est dans le tas d'autres universités) illustrant la fonction du générateur HSYNC / VSYNC, le mélangeur (de la même unité qui calcule le RVB en fonction de X / HCOUNT et Y / VCOUNT), ainsi que la sortie de HSYNC, VSYNC et RGB sur l'écran. L'image utilise un commutateur / multiplexeur entre trois mélangeurs - l'un dessine des rayures, un autre dessine un rectangle et le troisième dessine une image à l'écran tout en jouant au ping-pong: Dans le code, le mélangeur le plus simple ressemble à ceci. Il dessine des carrés multicolores à partir de mélanges de rouge, bleu et vert, ainsi que des lignes de couleurs pures:

Dans le code, le mélangeur le plus simple ressemble à ceci. Il dessine des carrés multicolores à partir de mélanges de rouge, bleu et vert, ainsi que des lignes de couleurs pures: De cette façon, vous pouvez dessiner une variété d'images statiques colorées. Voici les images que les élèves ont peintes dans une école d'été à Zelenograd immédiatement après une courte conférence expliquant comment le faire:

De cette façon, vous pouvez dessiner une variété d'images statiques colorées. Voici les images que les élèves ont peintes dans une école d'été à Zelenograd immédiatement après une courte conférence expliquant comment le faire: Eh bien, les écoliers peuvent encoder la fonction RVB (X, Y) et dessiner des images statiques. Mais que faire ensuite, quelle est la prochaine étape? Nous avons examiné la possibilité d'utiliser des matériaux du MIT, Digilent + Xilinx, Altera + Terasic et Steven Hugg, après quoi nous sommes arrivés à la conclusion qu'ils ne pouvaient pas être utilisés sous leur forme pure. Les laboratoires universitaires sont inclus dans le programme universitaire et le matériel des fournisseurs de FPGA n'est pas bien écrit et ne contient pas non plus de conseils sur la façon de changer le code au format d'une école d'été afin que les étudiants inventent leurs jeux. Le livre de Stephen Hugg a deux inconvénients qui sont le revers de ses vertus (vivacité et couleur):

Eh bien, les écoliers peuvent encoder la fonction RVB (X, Y) et dessiner des images statiques. Mais que faire ensuite, quelle est la prochaine étape? Nous avons examiné la possibilité d'utiliser des matériaux du MIT, Digilent + Xilinx, Altera + Terasic et Steven Hugg, après quoi nous sommes arrivés à la conclusion qu'ils ne pouvaient pas être utilisés sous leur forme pure. Les laboratoires universitaires sont inclus dans le programme universitaire et le matériel des fournisseurs de FPGA n'est pas bien écrit et ne contient pas non plus de conseils sur la façon de changer le code au format d'une école d'été afin que les étudiants inventent leurs jeux. Le livre de Stephen Hugg a deux inconvénients qui sont le revers de ses vertus (vivacité et couleur):Premièrement, Stephen Hugg n'a apparemment pas travaillé en tant que concepteur Verilog dans une entreprise d'électronique, donc il y a différentes choses dans son code qu'un verilogue professionnel ne ferait pas.

-, 8bitworkshop, , , , .

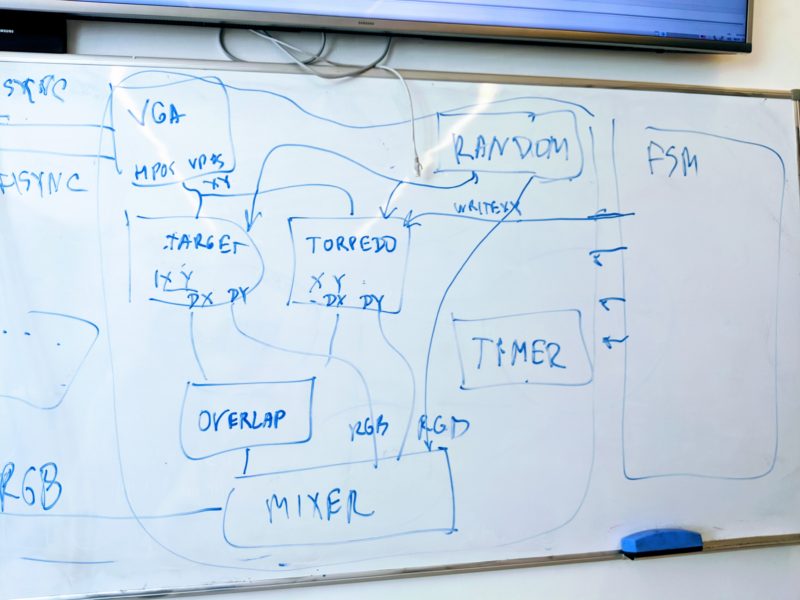

En général, le verilog de Stephen Hugg est à égalité avec la programmation des processeurs des anciennes consoles 8 bits d'Atari et de Nintendo. Ainsi, Hugg ne se concentre pas sur la formation des futurs superdesigners, mais sur les nostalgiques, les informaticiens rétro et autres reconstituteurs. La différence entre son environnement et les outils de conception professionnels est encore plus grande qu'entre l'environnement de programmation Arduino et les boîtes à outils pour STM32. Bien sûr, je ne propose pas de blâmer Cadence SimVision et Synopsys Design Compiler pour les écoliers pour des centaines de milliers de dollars, mais les écoliers pourraient bien obtenir des versions gratuites des outils professionnels Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, ainsi que Icarus Verilog, GTKWave et le edaplayground en ligne . com .J'ai relu le paragraphe précédent et j'ai pensé: mais Cadence SimVision pour l'école d'été de Zelenograd aurait pu être utilisé. Il est amélioré et plus pratique, à la fois de son concurrent direct Synopsys Design Vision Environment (DVE) * , et des fonds de Mentor Graphics (ModelSim gratuit et Questa payant), et de tous les outils bon marché et gratuits (IcarusVerilog, etc.) Si la succursale de Cadence à Moscou Le système de conception nous donnera le droit et le soutien nécessaires pour utiliser leur logiciel dans les écoles d'été de Zelenograd, personnellement, je serai pour intégrer cela dans le programme scolaire.* Pour DVE, par exemple, le texte dans la fenêtre source est bogué / sauté lorsque je l'exécute sous Ubuntu. Je dois redimensionner la fenêtre jusqu'à ce qu'elle cesse d'échouer. SimVision ne l'a pas.Voici le début du tutoriel SimVision (22 vidéos au total):Mais revenons aux jeux. Si ce n'est pas Stephen Hugg, alors quoi? J'ai écrit un exemple de jeu simple que j'ai utilisé dans une école d'été à Zelenograd . Les sources du jeu sont sur le github . Cela ressemble à ceci:Pendant deux semaines, les étudiants ont compris les principes de base de la conception au niveau des transferts de registres et ont commencé à créer leurs propres jeux, non triviaux:Parlons des détails techniques d'un exemple de jeu. Un module de jeu indépendant de la plate-forme peut être placé (instancié) dans le wrapper de n'importe quelle carte FPGA dotée d'un port VGA et de deux boutons. Si la carte est complètement nue, vous pouvez connecter un adaptateur pour VGA et des boutons via les fils GPIO (entrée / sortie à usage général). Le module de jeu comprend:

Bien sûr, je ne propose pas de blâmer Cadence SimVision et Synopsys Design Compiler pour les écoliers pour des centaines de milliers de dollars, mais les écoliers pourraient bien obtenir des versions gratuites des outils professionnels Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, ainsi que Icarus Verilog, GTKWave et le edaplayground en ligne . com .J'ai relu le paragraphe précédent et j'ai pensé: mais Cadence SimVision pour l'école d'été de Zelenograd aurait pu être utilisé. Il est amélioré et plus pratique, à la fois de son concurrent direct Synopsys Design Vision Environment (DVE) * , et des fonds de Mentor Graphics (ModelSim gratuit et Questa payant), et de tous les outils bon marché et gratuits (IcarusVerilog, etc.) Si la succursale de Cadence à Moscou Le système de conception nous donnera le droit et le soutien nécessaires pour utiliser leur logiciel dans les écoles d'été de Zelenograd, personnellement, je serai pour intégrer cela dans le programme scolaire.* Pour DVE, par exemple, le texte dans la fenêtre source est bogué / sauté lorsque je l'exécute sous Ubuntu. Je dois redimensionner la fenêtre jusqu'à ce qu'elle cesse d'échouer. SimVision ne l'a pas.Voici le début du tutoriel SimVision (22 vidéos au total):Mais revenons aux jeux. Si ce n'est pas Stephen Hugg, alors quoi? J'ai écrit un exemple de jeu simple que j'ai utilisé dans une école d'été à Zelenograd . Les sources du jeu sont sur le github . Cela ressemble à ceci:Pendant deux semaines, les étudiants ont compris les principes de base de la conception au niveau des transferts de registres et ont commencé à créer leurs propres jeux, non triviaux:Parlons des détails techniques d'un exemple de jeu. Un module de jeu indépendant de la plate-forme peut être placé (instancié) dans le wrapper de n'importe quelle carte FPGA dotée d'un port VGA et de deux boutons. Si la carte est complètement nue, vous pouvez connecter un adaptateur pour VGA et des boutons via les fils GPIO (entrée / sortie à usage général). Le module de jeu comprend:- Générateur de balayage VGA.

- Deux modules de travail parallèles pour les torpilles sprite et les cibles sprite.

- La machine d'état pour le scénario de jeu, avec les états "début", "guidage", "mouches", "victoire / défaite".

- Un module qui détermine si les sprites sont entrés en collision.

- Une minuterie pour régler la durée de l'effet visuel après avoir gagné (écran framboise clignotant) ou vaincu (écran jaune).

Pour la prochaine école, toutes ces images doivent être redessinées à l'aide de draw.io ou Lucidchart dans des diagrammes de microarchitecture normaux: vous

Pour la prochaine école, toutes ces images doivent être redessinées à l'aide de draw.io ou Lucidchart dans des diagrammes de microarchitecture normaux: vous devez également ajouter des chronologies dessinées avec WaveDrom au matériel scolaire pour montrer comment fonctionne le générateur de balayage VGA et comment le mini-pipeline calcule les coordonnées. chemin de données à l'intérieur des sprites:

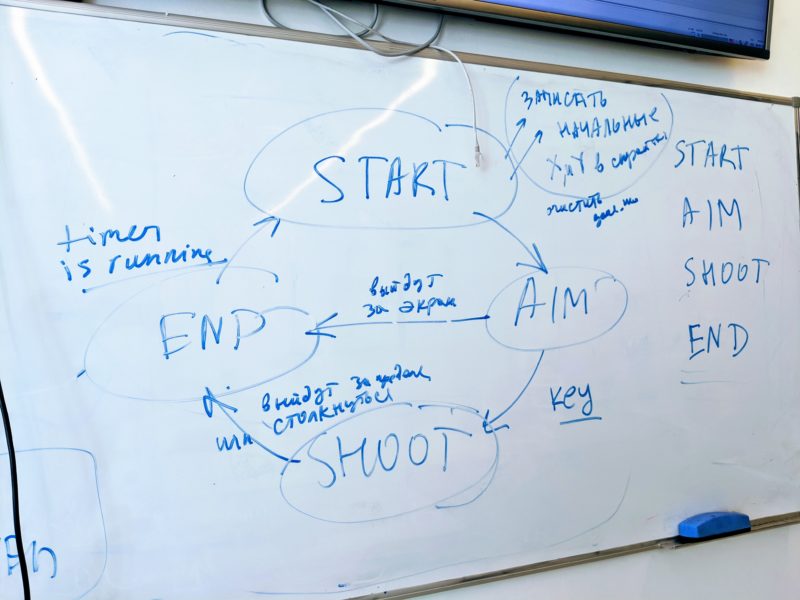

devez également ajouter des chronologies dessinées avec WaveDrom au matériel scolaire pour montrer comment fonctionne le générateur de balayage VGA et comment le mini-pipeline calcule les coordonnées. chemin de données à l'intérieur des sprites: Et bien sûr, vous devez dessiner des diagrammes de la machine à états finis. J'ai fait une douzaine de variantes de la machine à états finis de ce jeu, ici sur le plateau il y a une variante à quatre états:

Et bien sûr, vous devez dessiner des diagrammes de la machine à états finis. J'ai fait une douzaine de variantes de la machine à états finis de ce jeu, ici sur le plateau il y a une variante à quatre états: Pourquoi ai-je fait de nombreux choix? Même avec une machine aussi simple, vous pouvez comparer différents styles de leur codage sur un veril, ainsi qu'illustrer l'optimisation des états et du timing. Tout cela est demandé dans une interview pour un poste de concepteur de puces chez Apple, NVidia, Intel, AMD et d'autres sociétés. Par conséquent, cette zone doit être connue pour que les dents rebondissent. Il y a quelques bons articles de Clifford Cummings sur ce sujet:

Pourquoi ai-je fait de nombreux choix? Même avec une machine aussi simple, vous pouvez comparer différents styles de leur codage sur un veril, ainsi qu'illustrer l'optimisation des états et du timing. Tout cela est demandé dans une interview pour un poste de concepteur de puces chez Apple, NVidia, Intel, AMD et d'autres sociétés. Par conséquent, cette zone doit être connue pour que les dents rebondissent. Il y a quelques bons articles de Clifford Cummings sur ce sujet:- Article le plus récent de 2019: FiniteStateMachine (FSM) Design & Synthesis using SystemVerilog - Part I by Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

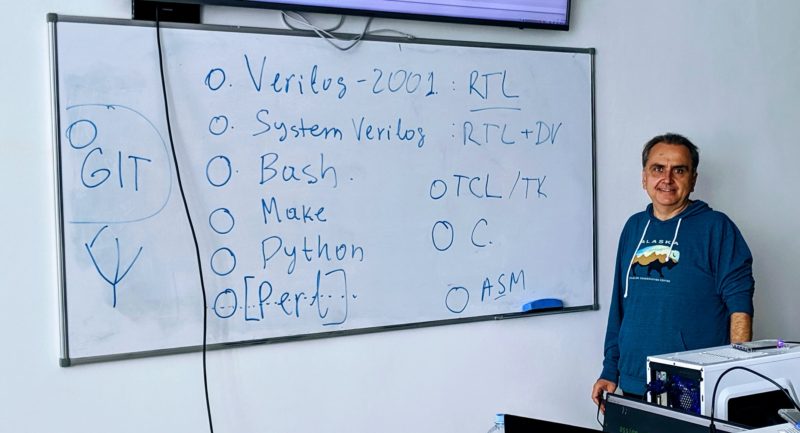

J'ai synthétisé différentes versions de la machine d'état du jeu en utilisant l'outil de compilation Synopsys Design Compiler le plus populaire de l'industrie et j'ai créé une telle tablette. Comme nous pouvons le voir, la version moderne de DC optimise tous les styles très efficacement, donc tirer des picosecondes sur les machines à états est possible, mais pas nécessaire. Bien qu'il soit possible pour des machines à états finis plus complexes, les astuces des articles de Cummings seront plus critiques: pendant les études à Zelenograd, nous avons également discuté du fait que dans la conception des puces, en plus des langages de description des équipements Verilog et VHDL, de nombreux langages auxiliaires sont utilisés:

pendant les études à Zelenograd, nous avons également discuté du fait que dans la conception des puces, en plus des langages de description des équipements Verilog et VHDL, de nombreux langages auxiliaires sont utilisés:Python est utilisé pour automatiser l'assemblage, la gestion de la régression et extraire des informations des rapports de synthèse et de génération de code, ainsi que des cuisines bash, make et autres Unix / Linux.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ et des bibliothèques comme SystemC sont utilisées pour écrire des modèles de blocs matériels au niveau des transactions. Les ingénieurs de vérification vérifient les blocs conçus sur le veril par rapport à ces modèles.

Si vous travaillez pour une entreprise de transformation, il est bon que vous connaissiez l'assembleur. Même si vous n'êtes pas un programmeur de bas niveau et pas un vérificateur, mais un concepteur de processeur au niveau des transferts de registres (Register Transfer Level - RTL).

Voici des liens pour ceux qui souhaitent utiliser Pearl comme préprocesseur pour Verilogue:- G. Spivey. EP3: un préprocesseur Perl extensible

- page de manuel vpp.pl

- Un préprocesseur Verilog

Un exemple d'utilisation de la perle verlog intégrée pour connecter 64 ports://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Ce serait bien si quelqu'un écrivait des scripts universels pour modéliser et synthétiser un exemple (pas nécessairement mon jeu) sur toutes les principales plates-formes de synthèse, simulation, débogage, analyse de la consommation d'énergie dynamique, conception physique, liaison pour toutes les cartes, etc. Cela pourrait être utilisé dans les écoles et les séminaires:

Ce serait bien si quelqu'un écrivait des scripts universels pour modéliser et synthétiser un exemple (pas nécessairement mon jeu) sur toutes les principales plates-formes de synthèse, simulation, débogage, analyse de la consommation d'énergie dynamique, conception physique, liaison pour toutes les cartes, etc. Cela pourrait être utilisé dans les écoles et les séminaires: Ici, vous pouvez avoir une question: pourquoi utiliser des séminaires Linux? Bien que Windows dispose également d'un environnement de modélisation et de synthèse pour les FPGA, Windows n'a pas pris racine dans l'industrie de la conception de puces de masse. Au début des années 1990, le marché des postes de travail pour les développeurs ASIC était divisé entre SunOS et HP / UX. Ensuite, les sociétés d'électronique ont joué pendant trois ans avec Windows NT, mais cela n'a pas fonctionné. Après cela, Synopsys et d'autres sociétés de logiciels de conception ont craché et sont passés à Linux - d'abord sur Red Hat, puis sur SuSE et Ubuntu. Je soupçonne, principalement à cause d'un tas de scripts sur la perle, le C-shell, etc., ainsi qu'à cause du travail à distance des développeurs via telnet et X Window.Par conséquent, pour mes séminaires, je vais avec un tas de SSD amorçables avec Lubuntu, sur lequel tous les logiciels nécessaires sont installés. J'utilise le démarrage hérité, mais récemment, il s'est avéré que de plus en plus d'ordinateurs nécessitent un démarrage UEFI. Apparemment, vous devrez créer un SSD amorçable avec démarrage UEFI.Les entreprises en évolution rapide utilisent CentOS au lieu de Red Hat. Peut-être que de nombreux outils de conception sont sous Debian, mais je ne l'ai pas testé.

Ici, vous pouvez avoir une question: pourquoi utiliser des séminaires Linux? Bien que Windows dispose également d'un environnement de modélisation et de synthèse pour les FPGA, Windows n'a pas pris racine dans l'industrie de la conception de puces de masse. Au début des années 1990, le marché des postes de travail pour les développeurs ASIC était divisé entre SunOS et HP / UX. Ensuite, les sociétés d'électronique ont joué pendant trois ans avec Windows NT, mais cela n'a pas fonctionné. Après cela, Synopsys et d'autres sociétés de logiciels de conception ont craché et sont passés à Linux - d'abord sur Red Hat, puis sur SuSE et Ubuntu. Je soupçonne, principalement à cause d'un tas de scripts sur la perle, le C-shell, etc., ainsi qu'à cause du travail à distance des développeurs via telnet et X Window.Par conséquent, pour mes séminaires, je vais avec un tas de SSD amorçables avec Lubuntu, sur lequel tous les logiciels nécessaires sont installés. J'utilise le démarrage hérité, mais récemment, il s'est avéré que de plus en plus d'ordinateurs nécessitent un démarrage UEFI. Apparemment, vous devrez créer un SSD amorçable avec démarrage UEFI.Les entreprises en évolution rapide utilisent CentOS au lieu de Red Hat. Peut-être que de nombreux outils de conception sont sous Debian, mais je ne l'ai pas testé. Pour les séminaires, j'utilise des cartes FPGA chinoises, dont l'une est tenue entre mes mains par une fille de Novossibirsk, Natasha, qui organise des soirées What-Where-When dans notre Silicon Valley .

Pour les séminaires, j'utilise des cartes FPGA chinoises, dont l'une est tenue entre mes mains par une fille de Novossibirsk, Natasha, qui organise des soirées What-Where-When dans notre Silicon Valley . Au mois de mars, j'ai traversé la faune californienne avec l'homme d'affaires russe Sergei Zorin, qui a amené une douzaine de planches ZEOWAA à Moscou, aux caractéristiques similaires à celle que Natasha tient entre leurs mains.Puisqu'il n'y aura probablement pas de séminaires à Zelenograd en raison du coronavirus cet été, je pense que je donnerai cette douzaine de frais aux écoliers de Moscou gratuitement (UPD: les écoliers d'autres villes peuvent aussi, bien qu'il y ait des problèmes supplémentaires avec la transmission). Avec deux conditions:

Au mois de mars, j'ai traversé la faune californienne avec l'homme d'affaires russe Sergei Zorin, qui a amené une douzaine de planches ZEOWAA à Moscou, aux caractéristiques similaires à celle que Natasha tient entre leurs mains.Puisqu'il n'y aura probablement pas de séminaires à Zelenograd en raison du coronavirus cet été, je pense que je donnerai cette douzaine de frais aux écoliers de Moscou gratuitement (UPD: les écoliers d'autres villes peuvent aussi, bien qu'il y ait des problèmes supplémentaires avec la transmission). Avec deux conditions:Avant d'obtenir une carte, vous devez parcourir les trois parties du cours en ligne «Comment fonctionnent les créateurs de nanopuces intelligentes» ( «Du transistor au microcircuit» , «Le côté logique des circuits numériques» , «Le côté physique des circuits numériques» ) et obtenir un certificat. Nous avons créé ce cours avec RUSNANO, ou plutôt sa fille éducative eNano, le projet STEMford.

, , , . , , , ( ) . , , .

, , .

Si vous souhaitez acheter un nouveau livre "Logical Synthesis" comme aide à un tel projet , alors pour les lecteurs de Habr, elle a un code promotionnel - Sintez_2020. À l'avenir, il serait bien de se débarrasser des cartes chinoises et de fabriquer une carte russe bon marché pour de tels exercices avec FPGA, avec une conception ouverte. Je vous souhaite la bienvenue si vous partagez vos réflexions dans les commentaires sur le logiciel de conception de cartes et les idées sur la façon de mieux concevoir et commercialiser une telle carte. Pour une utilisation de masse avec les écoliers, il est souhaitable que cela ne coûte pas plus de 30 $ ou 2000 roubles.

À l'avenir, il serait bien de se débarrasser des cartes chinoises et de fabriquer une carte russe bon marché pour de tels exercices avec FPGA, avec une conception ouverte. Je vous souhaite la bienvenue si vous partagez vos réflexions dans les commentaires sur le logiciel de conception de cartes et les idées sur la façon de mieux concevoir et commercialiser une telle carte. Pour une utilisation de masse avec les écoliers, il est souhaitable que cela ne coûte pas plus de 30 $ ou 2000 roubles. Si vous êtes étudiant et que vous êtes intéressé par la conception de microcircuits, vous pouvez aller à MIET, HSE MIEM, MEPhI, Université d'État de Moscou, Institut de physique et de technologie de Moscou ( Nikita Polyakov est engagé dans de tels exercices, MPEI, MISiS, ITMO, LETI, Samara University, certaines universités ukrainiennes (KNU, Chernihiv NTU, Kharkov KNURE) et d'autres universités. J'ai donc trouvé comment mon approche du comité de sélection MIET à Zelenograd était en cours de réparation:

Si vous êtes étudiant et que vous êtes intéressé par la conception de microcircuits, vous pouvez aller à MIET, HSE MIEM, MEPhI, Université d'État de Moscou, Institut de physique et de technologie de Moscou ( Nikita Polyakov est engagé dans de tels exercices, MPEI, MISiS, ITMO, LETI, Samara University, certaines universités ukrainiennes (KNU, Chernihiv NTU, Kharkov KNURE) et d'autres universités. J'ai donc trouvé comment mon approche du comité de sélection MIET à Zelenograd était en cours de réparation: Mais voici à quoi ressemble MIET à l'intérieur: Vous pouvez

Mais voici à quoi ressemble MIET à l'intérieur: Vous pouvez trouver un emploi là-bas juste en face de MIET à l'ONG ELVIS, qui s'occupe des caméras intelligentes et des puces satellites:

trouver un emploi là-bas juste en face de MIET à l'ONG ELVIS, qui s'occupe des caméras intelligentes et des puces satellites: Ou vous pouvez venir dans la Silicon Valley. Vous souhaitez obtenir un entretien avec Dolina? Entraînez-vous sur les cartes FPGA!

Ou vous pouvez venir dans la Silicon Valley. Vous souhaitez obtenir un entretien avec Dolina? Entraînez-vous sur les cartes FPGA!