Nous continuons d'évoluer vers la création de vrais appareils basés sur le complexe Redd FPGA. Pour un autre projet All-Hardware, j'ai besoin d'un simple analyseur logique, nous allons donc aller dans cette direction. Heureusement - et accédez à l'analyseur de bus USB (mais c'est toujours à long terme). Le cœur de tout analyseur est la RAM et une unité qui télécharge d'abord les données et les récupère ensuite. Aujourd'hui, nous allons le concevoir.Pour ce faire, nous maîtriserons le bloc DMA. En général, le DMA est mon sujet préféré. J'ai même fait un excellent article sur le DMA sur certains contrôleurs ARM . De cet article, il est clair que le DMA prend des cycles d'horloge du bus. Dans l'article actuel, nous examinerons comment les choses se passent avec le système de processeur basé sur FPGA.

Articles du cycle précédent Création de matériel

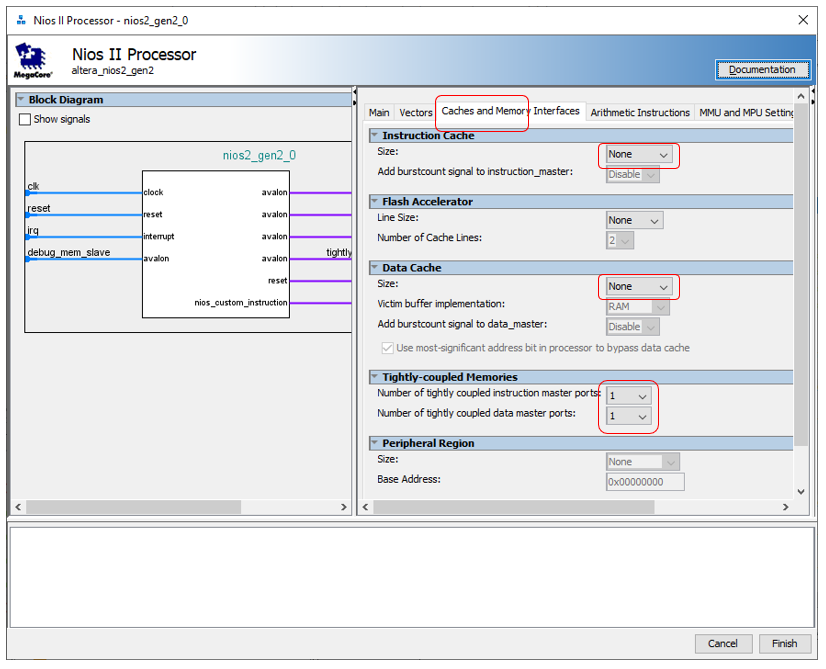

Nous commençons à créer le matériel. Afin de comprendre comment le bloc DMA entre en conflit au cours des cycles d'horloge, nous devrons effectuer des mesures précises à haute charge sur le bus Avalon-MM (Avalon Memory-Mapped). Nous avons déjà découvert que le pont Altera JTAG-Avalon-MM ne peut pas fournir des charges de bus élevées. Par conséquent, nous devons aujourd'hui ajouter un cœur de processeur au système afin qu'il accède au bus à grande vitesse. La procédure à suivre a été décrite ici . Par souci d'optimalité, désactivons les deux caches pour le cœur du processeur, mais créons un bus fortement connecté, comme nous l'avons fait ici . Ajoutez 8 kilo-octets de mémoire de programme et de mémoire de données. N'oubliez pas que la mémoire doit être à double port et avoir une adresse dans une plage spéciale (pour l'empêcher de sauter, verrouillez-la, nous en avons discuté les raisons ici ).

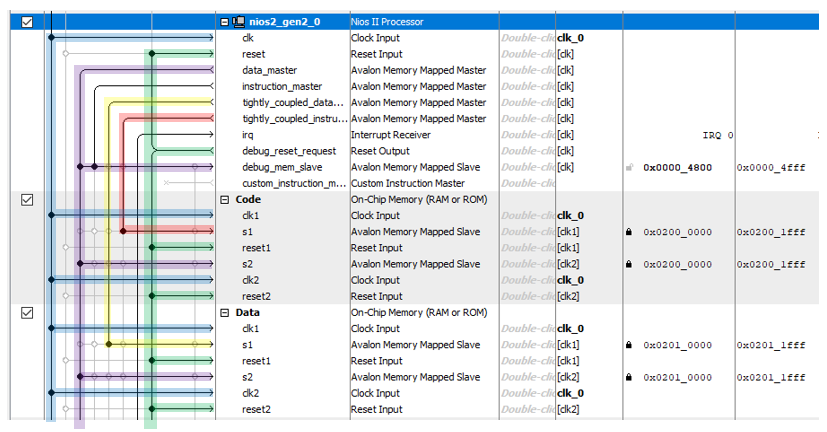

Ajoutez 8 kilo-octets de mémoire de programme et de mémoire de données. N'oubliez pas que la mémoire doit être à double port et avoir une adresse dans une plage spéciale (pour l'empêcher de sauter, verrouillez-la, nous en avons discuté les raisons ici ). Nous avons déjà créé le projet mille fois, il n'y a donc rien de particulièrement intéressant dans le processus de création lui-même (au contraire, toutes les étapes pour le créer sont décrites ici ).La base est prête. Maintenant, nous avons besoin d'une source de données que nous mettrons en mémoire. L'idéal est une minuterie qui tourne constamment. Si pendant une certaine mesure le bloc DMA n'a pas pu traiter les données, nous le verrons immédiatement par la valeur manquante. Eh bien, c'est-à-dire que si en mémoire il y a des valeurs 1234 et 1236, cela signifie que sur l'horloge, lorsque le temporisateur a émis 1235, le bloc DMA n'a pas transféré de données. Créer un fichierTimer_ST.sv avec un compteur aussi simple:

Nous avons déjà créé le projet mille fois, il n'y a donc rien de particulièrement intéressant dans le processus de création lui-même (au contraire, toutes les étapes pour le créer sont décrites ici ).La base est prête. Maintenant, nous avons besoin d'une source de données que nous mettrons en mémoire. L'idéal est une minuterie qui tourne constamment. Si pendant une certaine mesure le bloc DMA n'a pas pu traiter les données, nous le verrons immédiatement par la valeur manquante. Eh bien, c'est-à-dire que si en mémoire il y a des valeurs 1234 et 1236, cela signifie que sur l'horloge, lorsque le temporisateur a émis 1235, le bloc DMA n'a pas transféré de données. Créer un fichierTimer_ST.sv avec un compteur aussi simple:module Timer_ST (

input clk,

input reset,

input logic source_ready,

output logic source_valid,

output logic[31:0] source_data

);

logic [31:0] counter;

always @ (posedge clk, posedge reset)

if (reset == 1)

begin

counter <= 0;

end else

begin

counter <= counter + 1;

end

assign source_valid = 1;

assign source_data [31:24] = counter [7:0];

assign source_data [23:16] = counter [15:8];

assign source_data [15:8] = counter [23:16];

assign source_data [7:0] = counter [31:24];

endmodule

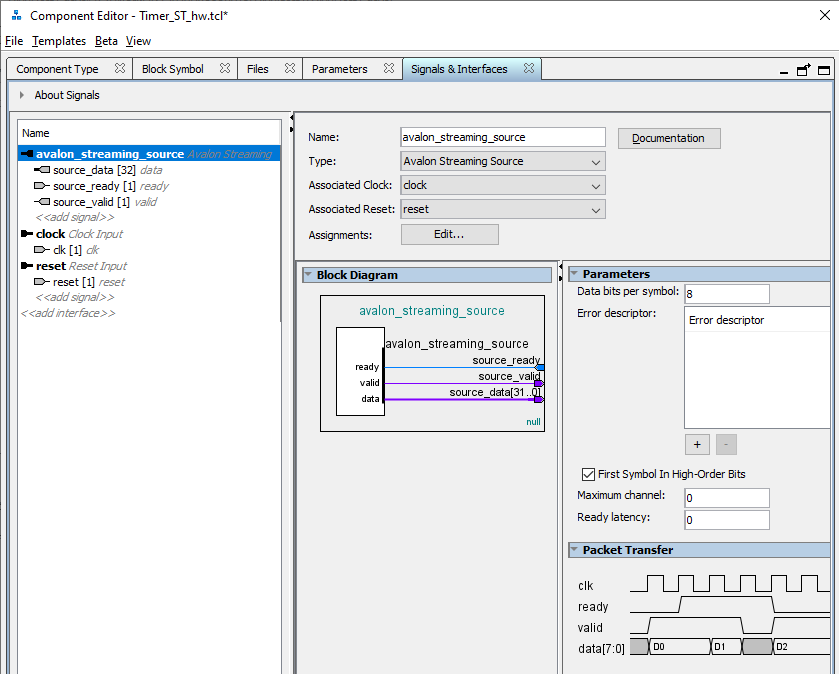

Ce compteur est comme un pionnier: il est toujours prêt (à la sortie source_valid est toujours un) et il compte toujours (sauf pour les moments de l'état reset). Pourquoi le module a exactement ces signaux - nous avons discuté dans cet article .Nous créons maintenant notre propre composant (comment cela se fait est décrit ici ). Automation a choisi par erreur le bus Avalon_MM pour nous. Remplacez-le par avalon_streaming_source et mappez les signaux comme indiqué ci-dessous: Excellent. Ajoutez notre composant au système. Maintenant, nous recherchons le bloc DMA ... Et nous n'en trouvons pas un, mais trois. Tous sont décrits dans le document Embedded Peripheral IP User Guide d'Altera (comme toujours, je donne des noms, mais pas des liens, car les liens changent toujours).

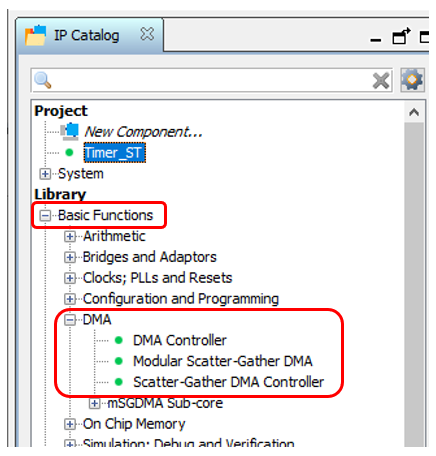

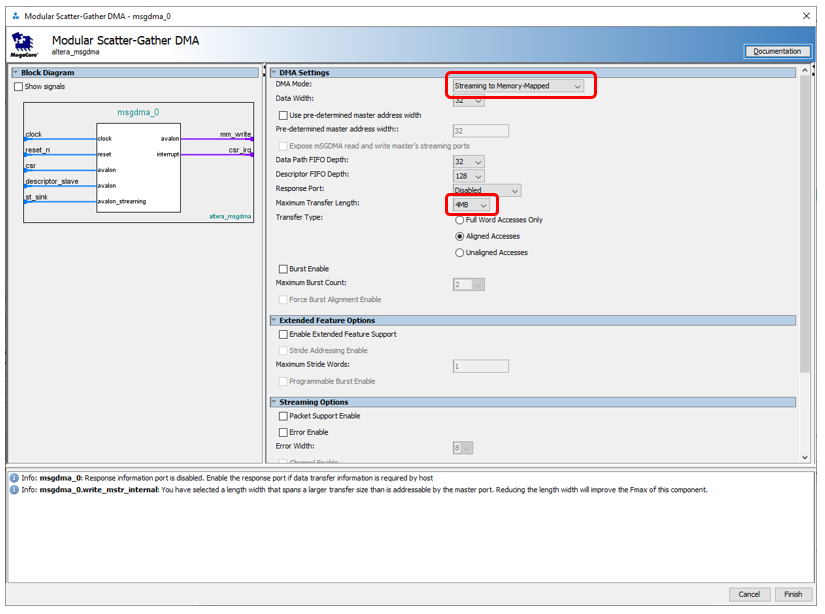

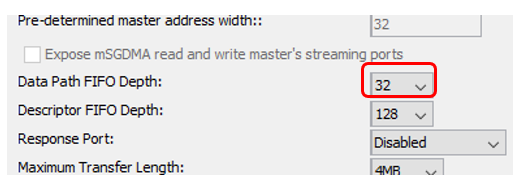

Excellent. Ajoutez notre composant au système. Maintenant, nous recherchons le bloc DMA ... Et nous n'en trouvons pas un, mais trois. Tous sont décrits dans le document Embedded Peripheral IP User Guide d'Altera (comme toujours, je donne des noms, mais pas des liens, car les liens changent toujours). Lequel utiliser? Je ne résiste pas à la nostalgie. En 2012, j'ai créé un système basé sur le bus PCIe. Tous les manuels d'Altera contenaient un exemple basé sur le premier de ces blocs. Mais lui avec le composant PCIe a donné une vitesse ne dépassant pas 4 mégaoctets par seconde. À cette époque, j'ai craché et écrit mon bloc DMA. Maintenant, je ne me souviens pas de sa vitesse, mais il a conduit les données des disques SATA à la limite des capacités des disques et SSD de l'époque. Autrement dit, j'ai aiguisé une dent sur ce bloc. Mais je ne glisserai pas dans une comparaison des trois blocs. Le fait est qu'aujourd'hui nous devons travailler avec une source basée sur Avalon-ST (Avalon Streaming Interface), et seul le bloc DMA Modular Scatter-Gather prend en charge ces sources . Ici, nous le mettons sur le diagramme.Dans les paramètres de blocage, sélectionnez le modeStreaming vers la mémoire mappée . De plus - je veux conduire les données du lancement au remplissage de la SDRAM, j'ai donc remplacé l'unité de transfert de données maximale de 1 kilo-octet à 4 mégaoctets. Certes, on m'a prévenu qu'à la fin, le paramètre FMax ne sera pas aussi chaud (même si vous remplacez le bloc maximum par 2 kilo-octets). Mais pour aujourd'hui, FMax est acceptable (104 MHz), puis nous le découvrirons. J'ai laissé les paramètres restants inchangés. Vous pouvez également définir le mode de transmission sur Full Word Access Only, ce qui augmentera FMax à 109 MHz. Mais nous ne nous battrons pas pour la performance aujourd'hui.

Lequel utiliser? Je ne résiste pas à la nostalgie. En 2012, j'ai créé un système basé sur le bus PCIe. Tous les manuels d'Altera contenaient un exemple basé sur le premier de ces blocs. Mais lui avec le composant PCIe a donné une vitesse ne dépassant pas 4 mégaoctets par seconde. À cette époque, j'ai craché et écrit mon bloc DMA. Maintenant, je ne me souviens pas de sa vitesse, mais il a conduit les données des disques SATA à la limite des capacités des disques et SSD de l'époque. Autrement dit, j'ai aiguisé une dent sur ce bloc. Mais je ne glisserai pas dans une comparaison des trois blocs. Le fait est qu'aujourd'hui nous devons travailler avec une source basée sur Avalon-ST (Avalon Streaming Interface), et seul le bloc DMA Modular Scatter-Gather prend en charge ces sources . Ici, nous le mettons sur le diagramme.Dans les paramètres de blocage, sélectionnez le modeStreaming vers la mémoire mappée . De plus - je veux conduire les données du lancement au remplissage de la SDRAM, j'ai donc remplacé l'unité de transfert de données maximale de 1 kilo-octet à 4 mégaoctets. Certes, on m'a prévenu qu'à la fin, le paramètre FMax ne sera pas aussi chaud (même si vous remplacez le bloc maximum par 2 kilo-octets). Mais pour aujourd'hui, FMax est acceptable (104 MHz), puis nous le découvrirons. J'ai laissé les paramètres restants inchangés. Vous pouvez également définir le mode de transmission sur Full Word Access Only, ce qui augmentera FMax à 109 MHz. Mais nous ne nous battrons pas pour la performance aujourd'hui. Donc. La source est, DMA est. Récepteur ... SDRAM? Dans les futures conditions de combat, oui. Mais aujourd'hui, nous avons besoin d'une mémoire aux caractéristiques connues. Malheureusement, la SDRAM doit envoyer périodiquement des commandes qui prennent plusieurs cycles d'horloge, et cette mémoire peut être occupée par la régénération. Par conséquent, au lieu de cela, nous allons maintenant utiliser la mémoire FPGA intégrée. Tout fonctionne pour elle en une seule étape, sans retards imprévisibles.Étant donné que le contrôleur SDRAM est à port unique, la mémoire intégrée peut également être utilisée exclusivement en mode port unique. C'est important. Le fait est que nous voulons écrire dans la mémoire à l'aide du maître de bloc DMA, mais d'un autre côté, nous voulons lire à partir de cette mémoire en utilisant le cœur du processeur ou le bloc Altera JTAG-to-Avalon-MM. La main tend la main et connecte les blocs d’écriture et de lecture à deux ports différents ... Mais vous ne pouvez pas! Il est plutôt interdit par les conditions du problème. Parce qu'aujourd'hui c'est possible, mais demain nous remplacerons la mémoire par une mémoire exclusivement à port unique. En général, nous obtenons un tel bloc de trois composants (minuterie, DMA et mémoire):

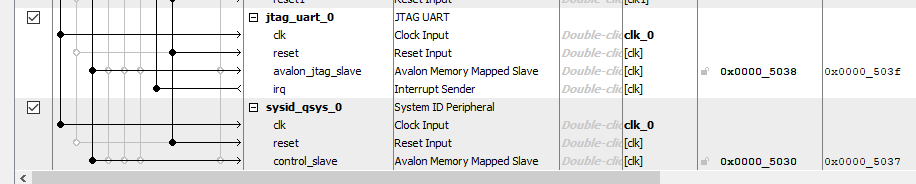

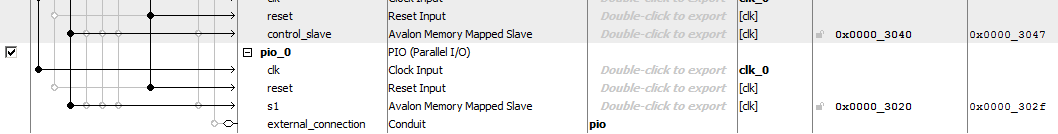

Donc. La source est, DMA est. Récepteur ... SDRAM? Dans les futures conditions de combat, oui. Mais aujourd'hui, nous avons besoin d'une mémoire aux caractéristiques connues. Malheureusement, la SDRAM doit envoyer périodiquement des commandes qui prennent plusieurs cycles d'horloge, et cette mémoire peut être occupée par la régénération. Par conséquent, au lieu de cela, nous allons maintenant utiliser la mémoire FPGA intégrée. Tout fonctionne pour elle en une seule étape, sans retards imprévisibles.Étant donné que le contrôleur SDRAM est à port unique, la mémoire intégrée peut également être utilisée exclusivement en mode port unique. C'est important. Le fait est que nous voulons écrire dans la mémoire à l'aide du maître de bloc DMA, mais d'un autre côté, nous voulons lire à partir de cette mémoire en utilisant le cœur du processeur ou le bloc Altera JTAG-to-Avalon-MM. La main tend la main et connecte les blocs d’écriture et de lecture à deux ports différents ... Mais vous ne pouvez pas! Il est plutôt interdit par les conditions du problème. Parce qu'aujourd'hui c'est possible, mais demain nous remplacerons la mémoire par une mémoire exclusivement à port unique. En général, nous obtenons un tel bloc de trois composants (minuterie, DMA et mémoire): Eh bien, et juste pour le proforma, je vais ajouter UT et sysid au système JTAG (bien que le second n'a pas aidé, je devais encore le conjurer avec un adaptateur JTAG). Ce que c'est et comment leur ajout résout de petits problèmes, nous avons déjà étudié. Je ne teinterai pas les pneus, tout est clair avec eux. Montrez simplement à quoi tout cela ressemble dans mon projet:

Eh bien, et juste pour le proforma, je vais ajouter UT et sysid au système JTAG (bien que le second n'a pas aidé, je devais encore le conjurer avec un adaptateur JTAG). Ce que c'est et comment leur ajout résout de petits problèmes, nous avons déjà étudié. Je ne teinterai pas les pneus, tout est clair avec eux. Montrez simplement à quoi tout cela ressemble dans mon projet: c'est tout. Le système est prêt. Nous attribuons des adresses, attribuons des vecteurs de processeur, générons un système (n'oubliez pas que vous devez enregistrer avec le même nom que le projet lui-même, puis il ira au niveau supérieur de la hiérarchie), l'ajouter au projet. Rendez la jambe de réinitialisation virtuelle, connectez clk à la jambe pin_25. Nous assemblons le projet, le versons dans le matériel ... Comment est-il, pauvre chose, dans le bureau vide à cause de la distance totale? ... C'est solitaire et effrayant pour elle, probablement, seul ... Mais j'étais distrait.

c'est tout. Le système est prêt. Nous attribuons des adresses, attribuons des vecteurs de processeur, générons un système (n'oubliez pas que vous devez enregistrer avec le même nom que le projet lui-même, puis il ira au niveau supérieur de la hiérarchie), l'ajouter au projet. Rendez la jambe de réinitialisation virtuelle, connectez clk à la jambe pin_25. Nous assemblons le projet, le versons dans le matériel ... Comment est-il, pauvre chose, dans le bureau vide à cause de la distance totale? ... C'est solitaire et effrayant pour elle, probablement, seul ... Mais j'étais distrait.Création d'une partie logicielle

Entraînement

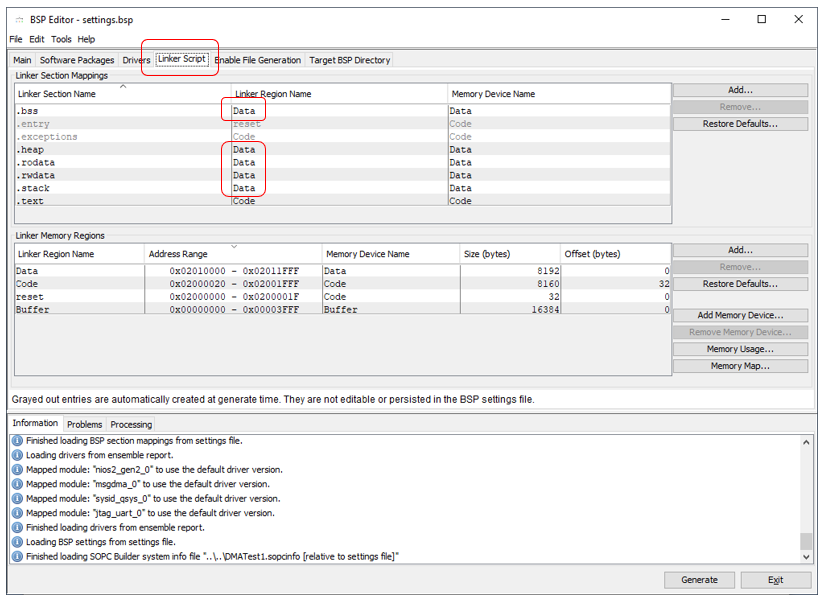

Dans l'éditeur BSP avec le mouvement habituel de la main, j'active le support C ++. J'ai si souvent inséré une capture d'écran de cette affaire que j'arrête de le faire. Mais une autre capture d'écran, bien qu'elle ait déjà été vue, est toujours aussi courante. Alors discutons-en une fois de plus. Nous nous souvenons que le système essaie de mettre les données dans la plus grande mémoire. Et tel est Buffer . Par conséquent, nous forçons tout sur les données :

Expérience de programme

Nous faisons un code qui remplit simplement la mémoire avec le contenu de la source (dans le rôle du compteur).Afficher le code#include "sys/alt_stdio.h"

#include <altera_msgdma.h>

#include <altera_msgdma_descriptor_regs.h>

#include <system.h>

#include <string.h>

int main()

{

alt_putstr("Hello from Nios II!\n");

memset (BUFFER_BASE,0,BUFFER_SIZE_VALUE);

// ,

IOWR_ALTERA_MSGDMA_CSR_CONTROL(MSGDMA_0_CSR_BASE,

ALTERA_MSGDMA_CSR_STOP_DESCRIPTORS_MASK);

// , ,

// , . .

// FIFO

IOWR_ALTERA_MSGDMA_DESCRIPTOR_READ_ADDRESS(MSGDMA_0_DESCRIPTOR_SLAVE_BASE,

(alt_u32)0);

IOWR_ALTERA_MSGDMA_DESCRIPTOR_WRITE_ADDRESS(MSGDMA_0_DESCRIPTOR_SLAVE_BASE,

(alt_u32)BUFFER_BASE);

IOWR_ALTERA_MSGDMA_DESCRIPTOR_LENGTH(MSGDMA_0_DESCRIPTOR_SLAVE_BASE,

BUFFER_SIZE_VALUE);

IOWR_ALTERA_MSGDMA_DESCRIPTOR_CONTROL_STANDARD(MSGDMA_0_DESCRIPTOR_SLAVE_BASE,

ALTERA_MSGDMA_DESCRIPTOR_CONTROL_GO_MASK);

// ,

IOWR_ALTERA_MSGDMA_CSR_CONTROL(MSGDMA_0_CSR_BASE,

ALTERA_MSGDMA_CSR_STOP_ON_ERROR_MASK

& (~ALTERA_MSGDMA_CSR_STOP_DESCRIPTORS_MASK)

&(~ALTERA_MSGDMA_CSR_GLOBAL_INTERRUPT_MASK)) ;

//

static const alt_u32 errMask = ALTERA_MSGDMA_CSR_STOPPED_ON_ERROR_MASK |

ALTERA_MSGDMA_CSR_STOPPED_ON_EARLY_TERMINATION_MASK |

ALTERA_MSGDMA_CSR_STOP_STATE_MASK |

ALTERA_MSGDMA_CSR_RESET_STATE_MASK;

volatile alt_u32 status;

do

{

status = IORD_ALTERA_MSGDMA_CSR_STATUS(MSGDMA_0_CSR_BASE);

} while (!(status & errMask) &&(status & ALTERA_MSGDMA_CSR_BUSY_MASK));

alt_putstr("You can play with memory!\n");

/* Event loop never exits. */

while (1);

return 0;

}

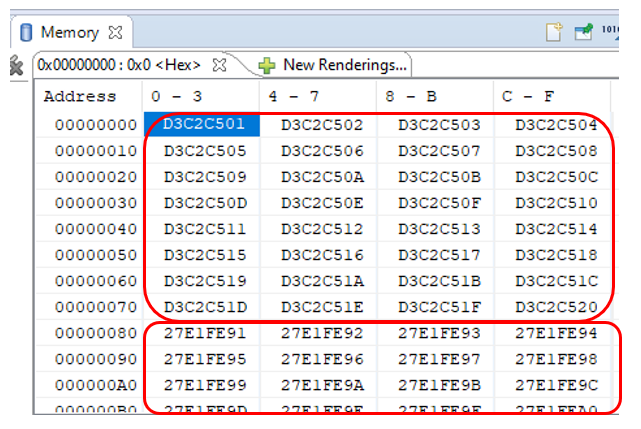

On commence, on attend le message "Tu peux jouer avec la mémoire!" , mettre le programme en pause et regarder la mémoire, à partir de l'adresse 0. Au début, j'avais très peur: à partir de l'adresse 0x80, le compteur change brusquement sa valeur. De plus, une très grande quantité. Mais il s'est avéré que tout allait bien. Chez nous, le compteur ne s'arrête jamais et est toujours prêt, et DMA a sa propre file d'attente de lecture anticipée. Permettez-moi de vous rappeler les paramètres du bloc DMA:

partir de l'adresse 0x80, le compteur change brusquement sa valeur. De plus, une très grande quantité. Mais il s'est avéré que tout allait bien. Chez nous, le compteur ne s'arrête jamais et est toujours prêt, et DMA a sa propre file d'attente de lecture anticipée. Permettez-moi de vous rappeler les paramètres du bloc DMA: 0x80 octets sont des mots de trente-deux bits 0x20. Seulement 32 décimales. Tout s'emboîte. Dans des conditions de débogage, ce n'est pas effrayant. Dans des conditions de combat, la source fonctionnera plus correctement (sa disponibilité sera réinitialisée). Par conséquent, nous ignorons simplement cette section. Dans d'autres régions, le compteur compte séquentiellement. Je ne montrerai que le fragment de vidage en largeur. Prenez un mot que je l'ai examiné dans son intégralité.

0x80 octets sont des mots de trente-deux bits 0x20. Seulement 32 décimales. Tout s'emboîte. Dans des conditions de débogage, ce n'est pas effrayant. Dans des conditions de combat, la source fonctionnera plus correctement (sa disponibilité sera réinitialisée). Par conséquent, nous ignorons simplement cette section. Dans d'autres régions, le compteur compte séquentiellement. Je ne montrerai que le fragment de vidage en largeur. Prenez un mot que je l'ai examiné dans son intégralité. Ne me faisant pas confiance, j'ai écrit un code qui vérifie automatiquement les données:

Ne me faisant pas confiance, j'ai écrit un code qui vérifie automatiquement les données: volatile alt_u32* pData = (alt_u32*)BUFFER_BASE;

volatile alt_u32 cur = pData[0x10];

int nLine = 0;

for (volatile int i=0x11;i<BUFFER_SIZE_VALUE/4;i++)

{

if (pData[i]!=cur+1)

{

alt_printf("Problem at 0x%x\n",i*4);

if (nLine++ > 10)

{

break;

}

}

cur = pData[i];

}

Il ne révèle également aucun problème.Essayer de trouver au moins quelques problèmes

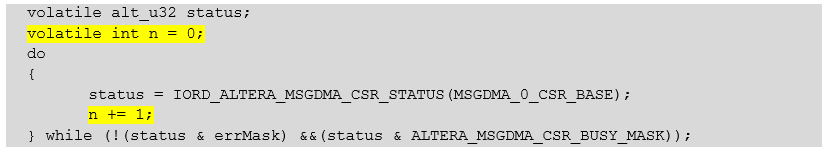

En fait, l'absence de problèmes n'est pas toujours bonne. Dans le cadre de l'article, j'avais besoin de trouver les problèmes, puis de montrer comment ils sont résolus. Après tout, les problèmes sont évidents. Un bus occupé ne peut pas transmettre de données sans retards! Il devrait y avoir des retards! Mais vérifions pourquoi tout se passe si bien. Tout d'abord, il peut s'avérer que le tout se trouve dans la FIFO du bloc DMA. Réduisez leur taille au minimum: tout continue de fonctionner! Bien. Assurez-vous que nous provoquons un nombre d'accès au bus supérieur à la dimension FIFO. Ajoutez un compteur d'accès:

tout continue de fonctionner! Bien. Assurez-vous que nous provoquons un nombre d'accès au bus supérieur à la dimension FIFO. Ajoutez un compteur d'accès:

Même texte: volatile alt_u32 status;

volatile int n = 0;

do

{

status = IORD_ALTERA_MSGDMA_CSR_STATUS(MSGDMA_0_CSR_BASE);

n += 1;

} while (!(status & errMask) &&(status & ALTERA_MSGDMA_CSR_BUSY_MASK));

À la fin du travail, il est de 29. C'est plus de 16. Autrement dit, le FIFO devrait déborder. Juste au cas où, ajoutons plus de lectures de registre d'état. N'aide pas.Avec chagrin, je me suis déconnecté du complexe distant de Redd, j'ai refait le projet sur ma maquette existante, à laquelle je peux me connecter avec un oscilloscope en ce moment (au bureau, personne n'est à distance, je ne peux pas atteindre l'oscilloscope). Ajout de deux ports à la minuterie: output clk_copy,

output ready_copy

Et les a nommés: assign clk_copy = clk;

assign ready_copy = source_ready;

En conséquence, le module a commencé à ressembler à ceci:module Timer_ST (

input clk,

input reset,

input logic source_ready,

output logic source_valid,

output logic[31:0] source_data,

output clk_copy,

output ready_copy

);

logic [31:0] counter;

always @ (posedge clk, posedge reset)

if (reset == 1)

begin

counter <= 0;

end else

begin

counter <= counter + 1;

end

assign source_valid = 1;

assign source_data [31:24] = counter [7:0];

assign source_data [23:16] = counter [15:8];

assign source_data [15:8] = counter [23:16];

assign source_data [7:0] = counter [31:24];

assign clk_copy = clk;

assign ready_copy = source_ready;

endmodule

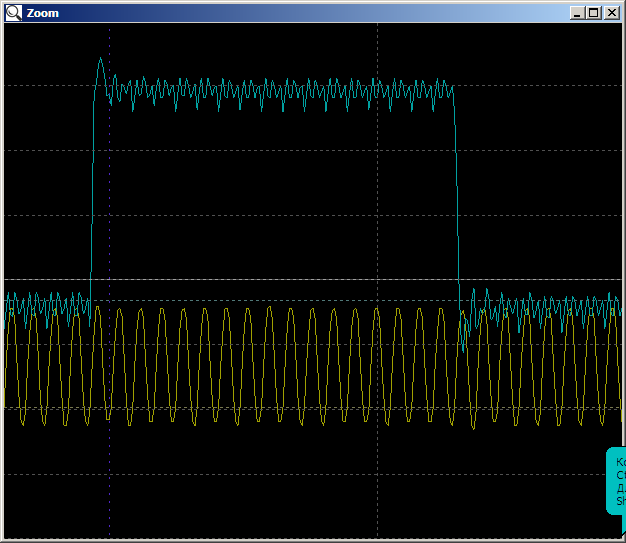

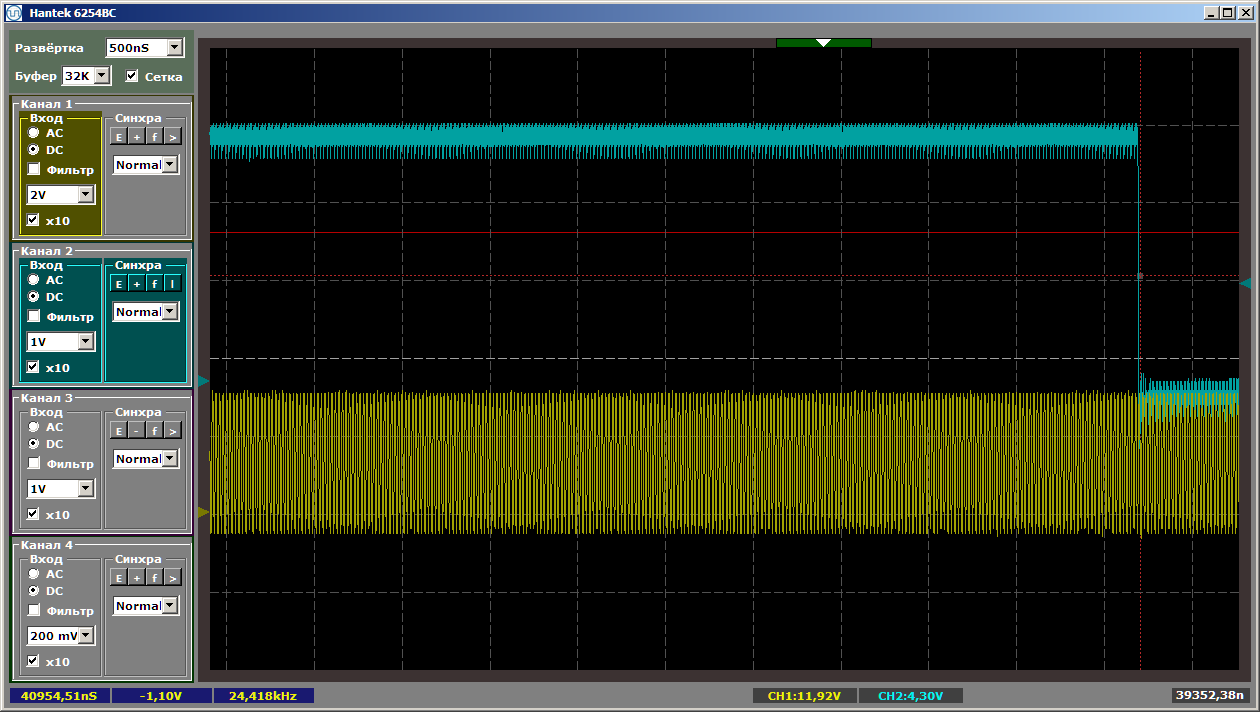

À la maison, j'ai un modèle plus petit avec un cristal, j'ai donc dû réduire l'appétit de la mémoire. Et il s'est avéré que mon programme primitif ne rentrerait pas dans une section de 4 kilo-octets. Donc, le sujet soulevé dans le dernier article est, oh, combien pertinent. Mémoire dans le système - à peine suffisante!Lorsque le début du programme, nous obtenons un prêt vague de 16 ou 17 mesures. Il est rempli avec le FIFO du bloc DMA. Le même effet qui m'a fait peur au début. Ce sont ces données qui formeront le très faux remplissage du tampon. Ensuite, nous avons une belle image à 40960 nanosecondes, soit 2048 cycles (avec un cristal domestique, le tampon a dû être réduit à 8 kilo-octets, soit 2048 mots de trente-deux bits). Voici son début:

Ensuite, nous avons une belle image à 40960 nanosecondes, soit 2048 cycles (avec un cristal domestique, le tampon a dû être réduit à 8 kilo-octets, soit 2048 mots de trente-deux bits). Voici son début: Voici la fin:

Voici la fin: Eh bien, et tout au long - pas un seul échec. Non, il était clair que cela arriverait, mais il y avait de l'espoir ...Peut-être devrions-nous essayer d'écrire sur le bus, et pas seulement de le lire? J'ai ajouté un bloc GPIO au système: y ai ajouté

Eh bien, et tout au long - pas un seul échec. Non, il était clair que cela arriverait, mais il y avait de l'espoir ...Peut-être devrions-nous essayer d'écrire sur le bus, et pas seulement de le lire? J'ai ajouté un bloc GPIO au système: y ai ajouté une entrée en attendant d'être prêt:

une entrée en attendant d'être prêt:

Même texte volatile alt_u32 status;

volatile int n = 0;

do

{

status = IORD_ALTERA_MSGDMA_CSR_STATUS(MSGDMA_0_CSR_BASE);

IOWR_ALTERA_AVALON_PIO_DATA (PIO_0_BASE,0x01);

IOWR_ALTERA_AVALON_PIO_DATA (PIO_0_BASE,0x00);

n += 1;

} while (!(status & errMask) &&(status & ALTERA_MSGDMA_CSR_BUSY_MASK));

Il n'y a aucun problème et c'est tout! Qui est à blâmer?Il n'y a pas de miracles, mais il y a des choses inexplorées

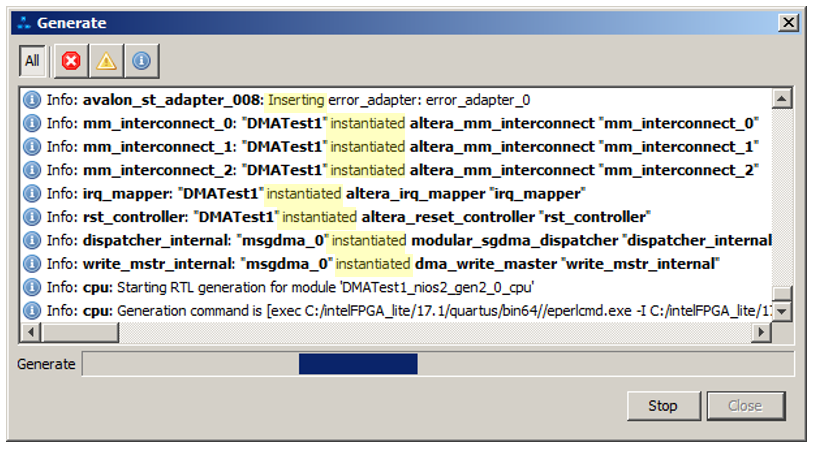

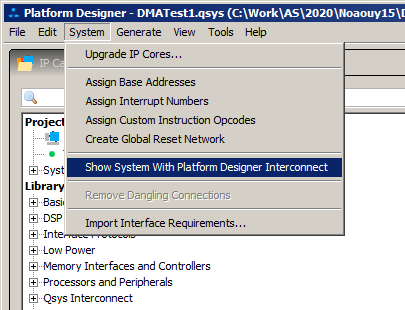

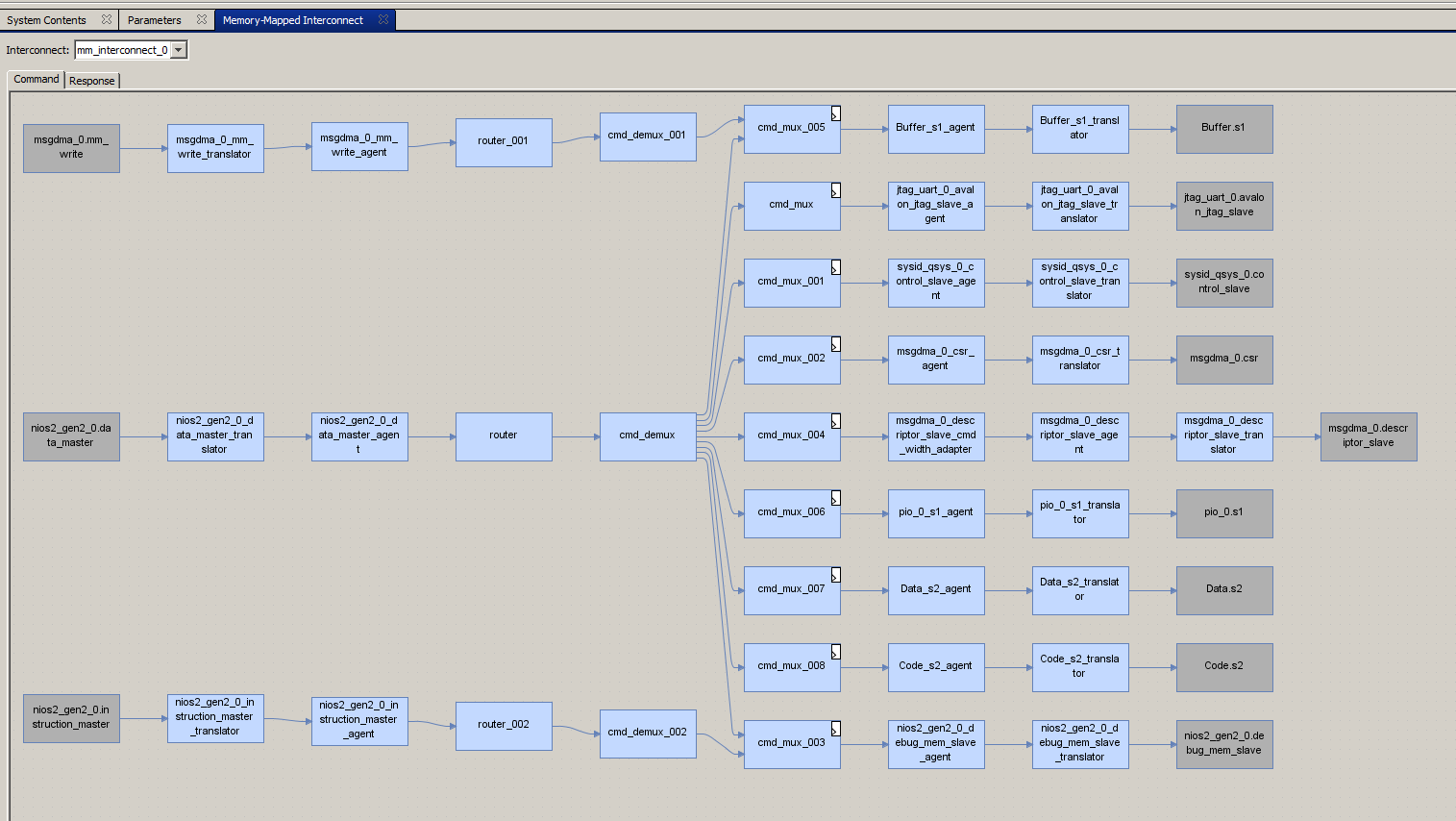

Qui est à blâmer? Avec peine, j'ai commencé à étudier tous les menus de l'outil Platform Designer et, semble-t-il , j'ai trouvé un indice. À quoi ressemble généralement un pneu? Ensemble de fils auxquels les clients sont connectés. Donc? Vraisemblablement. Nous le voyons dans les chiffres de l'éditeur. Juste, le deuxième objectif de l'article était de montrer comment le bus peut être divisé en deux segments indépendants, chacun fonctionnant sans interférer avec l'autre.Mais regardons les messages qui apparaissent lorsque le système est généré. Mettez en surbrillance les mots clés: Et il y a beaucoup de messages similaires: il est ajouté, il est ajouté. Il s'avère qu'après l'édition avec des stylos, beaucoup de choses supplémentaires sont ajoutées au système. Comment envisagez-vous un schéma dans lequel tout cela est déjà disponible? Je nage toujours dans ce domaine, mais nous pouvons obtenir la réponse la plus probable dans le cadre de l'article en choisissant cet élément de menu: L'

Et il y a beaucoup de messages similaires: il est ajouté, il est ajouté. Il s'avère qu'après l'édition avec des stylos, beaucoup de choses supplémentaires sont ajoutées au système. Comment envisagez-vous un schéma dans lequel tout cela est déjà disponible? Je nage toujours dans ce domaine, mais nous pouvons obtenir la réponse la plus probable dans le cadre de l'article en choisissant cet élément de menu: L' image ouverte est impressionnante en soi, mais je ne la donnerai pas. Et immédiatement,

image ouverte est impressionnante en soi, mais je ne la donnerai pas. Et immédiatement, je sélectionne cet onglet: Et là, nous voyons ce qui suit: Je vais

je sélectionne cet onglet: Et là, nous voyons ce qui suit: Je vais afficher plus grand le plus important:

afficher plus grand le plus important: Les pneus ne sont pas combinés! Ils sont segmentés! Je ne peux pas le justifier (peut-être que les experts me corrigeront dans les commentaires), mais il semble que le système ait inséré les interrupteurs pour nous! Ce sont ces commutateurs qui créent les segments de bus isolés, et le système principal peut fonctionner en parallèle avec l'unité DMA, qui peut actuellement accéder à la mémoire sans conflit!

Les pneus ne sont pas combinés! Ils sont segmentés! Je ne peux pas le justifier (peut-être que les experts me corrigeront dans les commentaires), mais il semble que le système ait inséré les interrupteurs pour nous! Ce sont ces commutateurs qui créent les segments de bus isolés, et le système principal peut fonctionner en parallèle avec l'unité DMA, qui peut actuellement accéder à la mémoire sans conflit!Nous provoquons de vrais problèmes

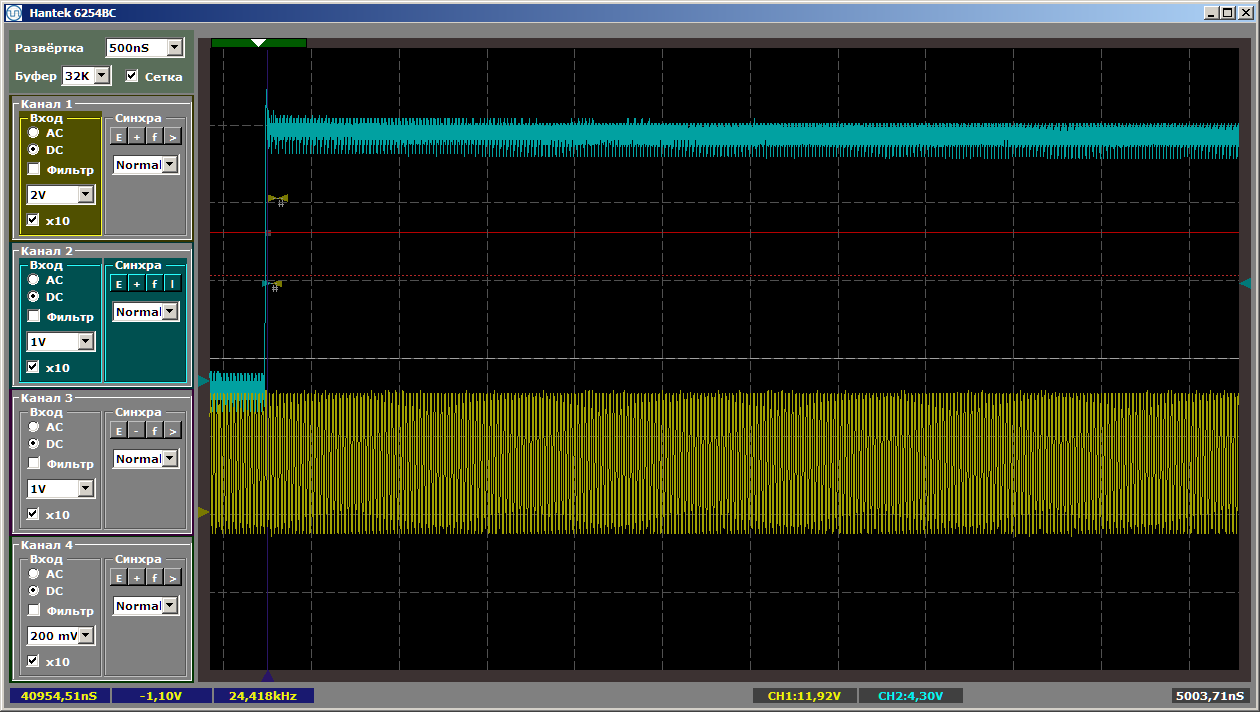

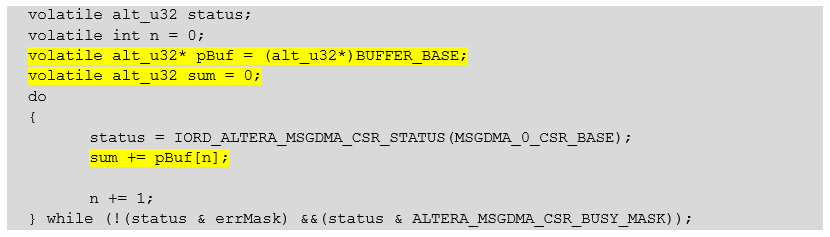

Ayant reçu toutes ces connaissances, nous concluons que nous pouvons très bien provoquer des problèmes. Cela est nécessaire pour s'assurer que le système de test peut les créer, ce qui signifie que l'environnement de développement les résout vraiment indépendamment. Nous ne ferons pas référence aux périphériques abstraits sur le bus, mais à la même mémoire tampon afin que le bloc cmd_mux_005 répartisse le bus entre le cœur du processeur et le bloc DMA. Nous réécrivons la fonction d'attente longue comme ceci:

Même texte volatile alt_u32 status;

volatile int n = 0;

volatile alt_u32* pBuf = (alt_u32*)BUFFER_BASE;

volatile alt_u32 sum = 0;

do

{

status = IORD_ALTERA_MSGDMA_CSR_STATUS(MSGDMA_0_CSR_BASE);

sum += pBuf[n];

n += 1;

} while (!(status & errMask) &&(status & ALTERA_MSGDMA_CSR_BUSY_MASK));

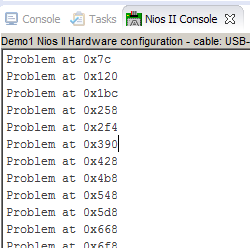

Et enfin, des creux sont apparus sur la forme d'onde! La fonction de vérification de la mémoire a également trouvé beaucoup d'omissions:

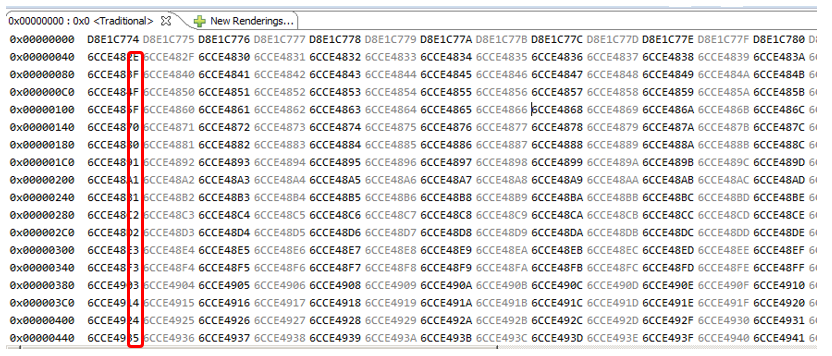

La fonction de vérification de la mémoire a également trouvé beaucoup d'omissions: Oui, et nous voyons très bien que les données sont déplacées d'une ligne à l'autre:

Oui, et nous voyons très bien que les données sont déplacées d'une ligne à l'autre: Et voici un exemple d'un mauvais endroit spécifique (6CCE488F est manquant):

Et voici un exemple d'un mauvais endroit spécifique (6CCE488F est manquant): Maintenant, nous voyons que l'expérience a été effectuée correctement, juste l'environnement de développement effectué optimisation pour nous. C'est le cas lorsque je prononce la phrase «Tous intelligemment blessé tout l'acier» non pas avec moquerie, mais avec gratitude. Merci aux développeurs Quartus pour cette question!

Maintenant, nous voyons que l'expérience a été effectuée correctement, juste l'environnement de développement effectué optimisation pour nous. C'est le cas lorsque je prononce la phrase «Tous intelligemment blessé tout l'acier» non pas avec moquerie, mais avec gratitude. Merci aux développeurs Quartus pour cette question!Conclusion

Nous avons appris à insérer un bloc DMA dans le système pour transférer des données de streaming vers la mémoire. Nous avons également veillé à ce que le processus de téléchargement d'autres appareils sur le bus n'interfère pas avec le processus de téléchargement. L'environnement de développement créera automatiquement un segment isolé qui s'exécutera en parallèle avec d'autres sections du bus. Bien sûr, si quelqu'un se tourne vers le même segment, les conflits et le temps passé à les résoudre sont inévitables, mais le programmeur peut très bien prévoir de telles choses.Dans le prochain article, nous allons remplacer la RAM par un contrôleur SDRAM, et le timer par une vraie "tête" et faire le premier analyseur logique. Est-ce que ça va marcher? Je ne sais pas encore. J'espère que les problèmes n'apparaissent pas.