Dans cette partie, nous verrons dans quelle direction vont les informations sur la touche enfoncée du clavier vers le CPU, il y aura beaucoup de photos et ce n'est pas la dernière partie. Je vais en parler du point de vue d'un programmeur qui écrit en mode utilisateur - programmes utilisateur, web, applications mobiles - donc, il peut y avoir des inexactitudes. Les personnes impliquées dans l'électronique ne trouveront probablement rien d'utile pour elles-mêmes. La première partie est ici .

for (int i = 0; i < COLSC; i++) {

SetPower(columns[i], 3.0 f);

for (int j = 0; j < ROWSC; j++) {

float power = GetPower(rows[j]);

if (power >= 3.0f - THRESHOLD) {

BYTE key = keys[i, j];

SendKey(key);

}

}

}

Chaque clé correspond à un code de numérisation, elle est normalisée et est un nombre à 8 bits, c'est-à-dire un octet. Par conséquent, lorsque la touche Y est enfoncée, le contrôleur de clavier devra envoyer le numéro 21 (0x15), et une fois relâché - 149 (0x95). Comment se déroule l'expédition? Vous avez sûrement travaillé avec JSON, des services Web ou envoyé des données entre les processus et vous savez que pour envoyer des données, vous devez sérialiser , c'est-à-dire se transformer en un tableau d'octets ou de texte formaté que le destinataire peut désérialiser , c'est-à-dire recréer un objet dans son espace d'adressage. Et qu'est-ce qui peut sérialiser des données à un niveau aussi bas? Nous devons transférer seulement 1 octet (8 bits). Pour l'avenir, je dirai que nous transmettrons les données petit à petit.En mathématiques, il existe une formule qui peut convertir n'importe quel nombre décimal auquel nous sommes habitués en une séquence de zéros et de uns et vice versa. Cette formule a trouvé une application dans la technologie informatique. Dans la première partie, j'ai mentionné avec désinvolture que la technologie analogique exploite les lois de la physique, tandis que le numérique fonctionne au niveau des zéros et des uns. Cela signifie qu'un téléphone analogique code le spectre entier de la voix humaine en une séquence d'ondes électromagnétiques, et un téléphone numérique utilise une puce qui convertit la voix humaine en données numériques, par exemple, dans des fichiers WAV, puis les transmet dans une séquence de zéros et de uns sous la forme d'ondes électromagnétiques. Seulement dans ce cas, au lieu de tout le spectre de la voix, seules deux valeurs doivent être représentées - 0 et 1. Elles peuvent être représentées par des ondes de longueurs différentes, de tensions différentesdes impulsions lumineuses à travers la fibre optique, des rayures noires et blanches sur du papier, des trous sur la carte perforée.Le code de balayage de la touche Y enfoncée en binaire ressemble à 0001 0101. Nous les transmettrons le long de la jambe du microcontrôleur qui est responsable des données ( DATA ). L'unité logique est 3,3 V ou plus, zéro logique- la tension est d'environ 0V. Voici le problème - comment passer trois zéros de suite? Pour ce faire, nous avons besoin d'un deuxième tronçon que nous appellerons CLOCK, lorsque sur celui-ci on veut dire que la session de transmission d'un bit a commencé, et zéro est terminée. Un tel changement de valeurs (tensions) se produira avec un certain intervalle de temps, disons 50 nanosecondes, car à l'autre extrémité il y a un deuxième microcontrôleur qui fonctionne à sa propre vitesse et écoute les jambes auxquelles CLOCK et DATA sont connectés dans une boucle sans fin. Dans cet exemple, je suppose que le clavier est connecté via le connecteur PS2, comme illustré ci-dessous. Via le port USB, l'algorithme de transfert sera différent. Comme vous pouvez le voir, le port PS2 a des broches appelées données, horloge.En plus d'eux, il y a également un contact par lequel le contrôleur de port PS2 distribue la tension de 5 V nécessaire au fonctionnement au clavier et un contact de masse, qui est simplement affiché sur le corps du clavier. Les autres contacts ne sont pas utilisés.Le port PS / 2 est appelé bus série , car il transmet les bits un par un (une séquence de bits). Le port parallèle transmet des données à la fois à plusieurs contacts et peut transférer par exemple un octet (8 bits) à la fois pour une session de transfert de données.Quelle est la différence entre un port, un bus et un protocole? Un bus, comme un port, est un ensemble de contacts (câblage) et un accord sur la façon de les utiliser, seul le port a une connexion pour connecter des périphériques externes, et le bus est utilisé pour communiquer des composants sur la carte mère. Un port est essentiellement un bus avec un connecteur au milieu. Un protocole est une interaction par le biais de contacts. Dans l'exemple avec PS / 2, c'était l'ordre de transfert des données via les contacts Horloge et Données.

Auparavant, le microcontrôleur Intel 8042 était très courant et était utilisé à la fois dans le clavier et comme contrôleur de port PS2, c'est-à-dire deux puces identiques ont échangé des données. Le pilote de port PS2 sous Windows s'appelle 8042prt.sys.

En fait, nous ne transmettons pas 8 bits, mais 11, car les données sont transmises sous forme de paquet de données ou de message . 3 bits supplémentaires indiquent le début et la fin des données - un zéro au début et 0 1 à la fin, un tel protocole pour transférer des données de l'appareil vers l'hôte dans PS2. Cela peut ressembler à la fonction SendKey en pseudo-code, si vous préférez comprendre le code. Il envoie des données sur la touche enfoncée via le bus PS2.

void SendBit(BYTE bit) {

float power = (bit != 0) ? 3.3f : 0.0f;

SetPower(DATA, power);

SetPower(CLOCK, 3.3f);

Sleep(50);

SetPower(CLOCK, 0.0f);

Sleep(50);

}

void SendData(BYTE data) {

SendBit(0);

for (BYTE i = 0; i < sizeof(BYTE); i++) {

BYTE bit = (data >> i) & 1;

SendBit(bit);

}

SendBit(0);

SendBit(1);

}

Il n'est pas toujours nécessaire de régler manuellement la tension sur chaque branche individuellement pour le transfert de données. Dans certains cas, la valeur stockée dans le registre est automatiquement affichée sur les contacts.

Sur le graphique, un tel transfert de données sera visualisé comme suit. Le temps est le long de l'axe X et la tension est le long de l'axe Y.En technologie analogique, le signal peut être déformé, c'est-à-dire le fil n'est connecté à rien, mais le voltmètre affiche 0,5 V sur lui en raison du fait qu'il y a un champ électromagnétique à proximité. Par conséquent, le concept de tension de seuil est utilisé. Si la tension est inférieure au seuil, alors nous supposons que nous avons obtenu un zéro logique, sinon l'unité. Compte tenu des distorsions possibles, le code de balayage de la touche Y enfoncée peut se présenter comme suit:Avant d'examiner de plus près comment les données du clavier parviennent au processeur, parlons des micropuces , des bus et des cartes mères .Microcontrôleurs et microcircuits

Le microcontrôleur peut exécuter un programme qui y est cousu, dispose d'une certaine quantité de mémoire RAM et d'un emplacement pour stocker les données et le code du programme. Dans la puce, le programme peut être défini au stade de la conception. La création manuelle d'un circuit électrique mettant en œuvre un algorithme prend beaucoup de temps et, par conséquent, un langage de programmation spécial appelé VHDL (Hardware Description Language) peut être utilisé pour concevoir des microcircuits . Il s'agit d'un langage de programmation de haut niveau qui se traduit par un plan de circuit, il est exécuté via un programme qui trouve l'emplacement optimal des éléments radio sur la carte et est finalement réalisé sous forme physique. Les images sont à but illustratif uniquement.Comment les données et les commandes sont-elles représentées dans les micropuces et les microcontrôleurs? La base de la technologie informatique est un transistor, que l'humanité a appris à fabriquer dans des dimensions microscopiques. Un transistor est un tel élément radio qui a trois jambes: une entrée, une sortie et entre elles une commande qui ouvre ou ferme le courant entre deux jambes. La figure ci-dessous illustre le fonctionnement du transistor, l'eau illustre le courant.La tension est appliquée à la jambe d'entrée, si le contrôle a une tension, alors le courant passe à la sortie, sinon il y aura 0V. Ayant 8 transistors, dont chacun a une LED connectée à la jambe de sortie qui s'allume ou non, nous pouvons imaginer 256 combinaisons uniques (2 à la puissance de 8). Lapochki sont interprétés de droite à gauche, ainsi que les nombres décimaux. Les chiffres inférieurs sont à droite.Ceux. une ampoule représente un bit d'information (0 ou 1), et huit de ces ampoules correspondent à un octet. Il est possible de construire des opérateurs logiques ET, OU, NON, XOR sur des transistors.Par exemple, dans les circuits de l'opérateur ET (à gauche dans l'image ci-dessus), la sortie n'aura de tension que si les deux tensions d'entrée ne sont pas nulles. Quelqu'un a déjà inventé des algorithmes d'addition, de multiplication, de division et de soustraction basés sur des opérations logiques et des décalages de bits. Les fabricants de puces doivent simplement les mettre en œuvre. Le fonctionnement de l'algorithme d'addition au niveau du bit est illustré ci-dessous; nous ne l'analyserons pas:Les nanotransistors sont microscopiques et peuvent être placés sur la carte par millions. Le processeur Intel est illustré ci-dessous et à quoi pourrait ressembler l'un de ses cœurs. L'image est illustrative.Les microcircuits peuvent contenir un microcontrôleur sur la même carte et dans le même boîtier.Pneus

En règle générale, dans les manuels, les pneus sont représentés par des flèches en gras, comme dans l'image ci-dessous. Ceci est fait pour ne pas dessiner toutes les connexions des contacts, qui peuvent être nombreuses. Le fonctionnement du bus PS2 est très simple, tout ce dont vous avez besoin est de trois broches. Mais il existe des bus qui, par exemple, ont 124 contacts pour le transfert de données.Il existe les types de pneus suivants:- Données - les bits sur ces contacts sont interprétés comme des données: nombre, symbole, partie d'une image ou autres données binaires. La largeur du bus affecte le débit, le nombre de bits transmis par seconde

- Adresses - les bits sur ces broches sont interprétés comme une adresse physique en mémoire. La largeur de ce bus détermine la capacité RAM maximale prise en charge.

- — . CPU RAM I/O.

- . , . ATX 24 Pin 12V PSU Connector, .

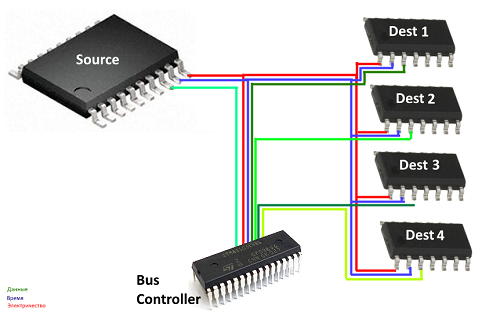

Un pneu peut être constitué de substrats , c'est-à-dire certains contacts sont utilisés pour les données, d'autres pour les adresses, d'autres pour le contrôle et les contacts auxquels l'alimentation est transmise. L'approche lorsque les mêmes contacts sont utilisés alternativement pour transmettre à la fois des données et des adresses s'appelle le multiplexage . Par exemple, le processeur Intel 8086 a un bus de données et d'adresses de 20 bits, sur le diagramme des broches ses contacts sont indiqués par AD0-AD19 (jambes 16-2 et 39-35).Dans un cas plus complexe, nous pouvons avoir plusieurs microcircuits connectés aux mêmes contacts. Pour une communication normale, ils ont besoin d'une puce supplémentaire qui déterminera qui à quel moment peut les utiliser, il s'agit d'un contrôleur de bus. Dans la figure ci-dessous, un bus sphérique dans le vide: quatre microcontrôleurs identiques transmettent des données au microcontrôleur grand public via le contrôleur de bus. Le fil rouge est la tension que le contrôleur de bus distribue à toutes les puces qui lui sont connectées. Les données sont transmises via les fils verts et la «négociation» avec le contrôleur de bus est effectuée, et le fil bleu est Horloge, à travers laquelle le contrôleur de bus synchronise la communication des contrôleurs, car ils peuvent fonctionner à différentes vitesses. Si l'unité logique est sur le fil bleu, la puce autorisée à utiliser le bus peut effectuer un acte d'interaction avec le monde extérieur - lire un peu, par exemple.

- Lent - clavier, disque dur, carte réseau, audio, etc.

- Rapide - CPU, RAM, GPU.

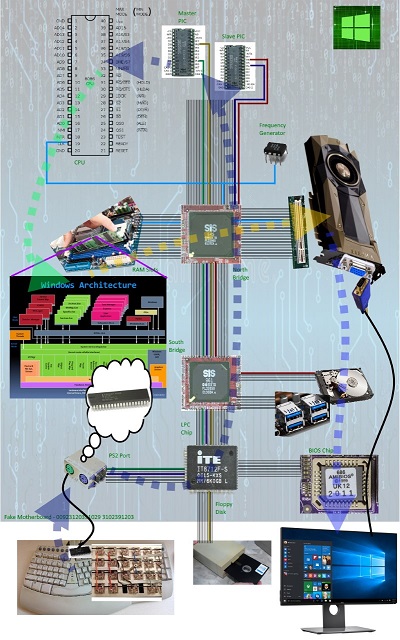

Sur la base de cette division, la carte mère a deux puces principales - le pont sud , qui coordonne le travail de tous les appareils lents, et le pont nord, pour la coordination des appareils rapides. Dans les ordinateurs modernes, le Northbridge est situé dans le CPU lui-même, et le Southbridge peut être appelé le Platform Controller Hub, mais cela ne change pas l'essence. Ces deux ponts sont reliés entre eux par un bus grâce auquel ils s'informent mutuellement des événements importants. Le générateur d'horloge par lequel le processeur, la RAM et la carte graphique synchronisent leur travail, le même fil bleu, est particulièrement intéressant . Overclockingcela modifie essentiellement les paramètres du BIOS afin que la synchronisation se produise plus souvent, tandis que le matériel, principalement le CPU, chauffera plus fort, consommera plus d'énergie et développera plus rapidement ses ressources. L'inverse est l' overclocking , lorsque la vitesse diminue pour économiser la batterie ou réduire le bruit.Un chipset est un ensemble de puces qui ont toutes été conçues pour fonctionner les unes avec les autres. Ils assurent la communication entre les composants de la carte mère et fournissent des fonctionnalités telles que des minuteries. Le jeu de puces fonctionne avec une seule marque de processeur, AMD ne peut pas être inséré dans la carte mère avec le chipset Intel, ils ont même des contacts différents. Le schéma de la carte mère est présenté ci-dessous:Vous voulez un exemple d'encapsulation matérielle? Les chipsets Intel ont une puce appelée Super IO , elle est illustrée dans l'image ci-dessous et est connectée au pont sud via le bus LPC. LPC est le nom intelligent pour le câblage CLOCK, DATA, VCC (POWER). Cette puce contient l'émulation de toutes les anciennes puces jamais utilisées pour les périphériques, y compris la puce 8042 utilisée pour le port PS2. Il existe également un émulateur de contrôleur de port pour Floppy et d'autres reliques qui interfèrent avec la progression. Dans le schéma général de la carte mère, Super IO et le bus LPC sont indiqués ci-dessus .Le port PS2 moderne se connecte directement à la puce Super I / O. Le vert est le clavier, le violet est la souris. Auparavant, il était connecté au microcontrôleur Intel 8042.La carte mère est en diélectrique, c'est-à-dire matériau qui ne conduit pas de courant. Le courant ne peut passer que sur les lignes imprimées sur la carte. La carte mère a de nombreuses couches, chacune ayant ses propres contacts imprimés et donc si vous percez la carte mère là où les lignes ne sont pas visibles, vous pouvez la gâcher en endommageant les contacts invisibles à l'intérieur de la carte. Vous pouvez maintenant regarder de plus près le processus de distribution des données de la PS2 vers le CPU.La route de la PS2 au processeur

En règle générale, l'architecture informatique est considérée sur le processeur 8086. D'une part, cela est correct, car il est assez simple par rapport aux processeurs modernes, et d'autre part, il est faux, car il est ancien et ne reflète pas l'architecture d'une machine moderne. Intel 8086 n'avait pas besoin de ponts, car il était si lent qu'il pouvait fonctionner avec des périphériques sur un bus, c'est-à-dire à une fréquence. Je ne connais pas les processeurs et jeux de puces modernes, je vais donc les expliquer sur des fictifs qui ressemblent à de vrais. Dans mon exemple, il y aura un CPU fictif très similaire à Intel 8086. La puce Super IO a plus de cent contacts et il existe de la documentation sur Internet, mais je ne vois pas l'intérêt de trier les broches que le clavier et le bus LPC utilisent réellement pour communiquer avec South Bridge. L'essentiel est le principe, qui peut être mis en œuvre de différentes manières.Jetons un rapide coup d'œil à la photo pour nous souvenir que nous sommes déjà passés. Les flèches vertes indiquent le chemin que nous allons emprunter.Ainsi, les données du clavier sont déjà arrivées au contrôleur de port PS2, qui était autrefois une puce Intel 8042, et est maintenant émulé par une puce Super IO. Et maintenant, analysons la suite des actions sur ma carte mère fictive avec un processeur fictif. Le contrôleur PS2 a reçu un code de balayage de la touche Y enfoncée et fournit maintenant une tension au signal de contact (ligne violette, voir l'image ci-dessous) sur laquelle le contrôleur d'interruption programmable doit notifier les données du clavier. Ce signal est transmis d'une puce à l'autre jusqu'à ce que le North Bridge le transmette au gestionnaire d'interruption.Le contrôleur d'interruption programmable est une puce Intel 8259 dans laquelle 8 branches (leurs noms IRQ0-IRQ7) sont réservées pour recevoir des notifications de certains ports ( I nterrupt R e Q uest). Un clavier est lié à la broche IRQ1, IRQ7 à une imprimante, une disquette à une broche, une carte son, des ports parallèles et autres . Bien sûr, il peut y avoir beaucoup plus de huit appareils, donc une technique telle que la cascade a été utilisée lorsqu'un autre PIC similaire a été connecté à une jambe avec le nom IRQ2, auquel le décompte n'a pas commencé à partir de 0, mais 7. La souris est liée à IRQ12, c'est-à-dire pied IRQ5 sur le deuxième PIC.Le contrôleur d'interruption doit maintenant informer le CPU de l'événement sur le clavier. Cela se produit comme suit:- INT (Interrupt) , INTR (Interrupt Request) . CPU , , .. . , . exception .

- INTR, .

- ( D0-D7) , . PIC ( IRQ).

, ? . . — (x, y, z, w). . - CPU AD0-AD7 , . IDT (Interrupt Descriptior Table) , , . CPU .

. . , IDT C# .

struct IDT_entry{

unsigned short int offset_lowerbits;

unsigned short int selector;

unsigned char zero;

unsigned char type_attr;

unsigned short int offset_higherbits;

};

struct IDT_entry IDT[256];

- , INTA (Interrupt Acknowledged).

Le gestionnaire d'interruption du clavier dans le code le plus simple ressemblera à ceci. Il appelle une commande qui signale la fin du traitement d'interruption, c'est-à-dire envoie un signal au pied INTA.void irq1_handler(void) {

outb(0x20, 0x20);

}

Vous pouvez en savoir plus sur la configuration de la table des vecteurs d'interruption sur osdev .Nous savons maintenant comment l'interruption s'est produite, mais nous ne savons pas comment le gestionnaire d'interruption lit les informations sur la touche enfoncée. D'un point de vue logiciel, le port PS2 est deux registres, seulement ils ne sont pas accessibles par des noms ou des adresses en mémoire par le numéro de port d' E / S . Ces deux registres à un octet sont affectés aux ports 0x60 et 0x64, le premier (0x60) contiendra le code de balayage de la clé. Le deuxième port est utilisé pour transférer l'état et les commandes vers le port PS2 (pas le clavier!). Le jeu d'instructions d'architecture x86 a la commande IN storeTo , fromPortNumqui lit la valeur du port d'E / S spécifié dans le registre spécifié. Par exemple, EN AL, 0x60 enregistrera les données du clavier dans le registre AL. Cela pourrait fonctionner comme ceci:- Dans le processeur que nous considérons, il existe des jambes AD0-AD20, elles peuvent être utilisées pour indiquer l'adresse et les données. Il s'agit à la fois d'un bus de données et d'un bus d'adresses. En plus d'eux, il y a un certain nombre de jambes de contrôle, par exemple, la broche n ° 28 (S2), dont la valeur indiquera au pont nord où la lecture aura lieu - à partir de la mémoire ou d'un périphérique d'entrée / sortie. La commande IN définit la valeur ici en parlant du périphérique d'E / S.

- CPU (- AD0-AD20) 0110 0000, 0x60. CPU , . , - , - . 0x60 SuperIO , - .

- Super IO . 0x60 PS2, .

- . Intel 8042, SuperIO, LPC , . .. , .

- CPU (- 8 AD0-AD20).

- CPU AL. .

Tout cet algorithme fonctionne à l'échelle nanoseconde et s'exécute donc presque instantanément, même si le processeur a mis un certain temps à attendre l'opération d'E / S.Comme vous le comprenez maintenant, la lecture à partir de périphériques externes, même comme la mémoire RAM, etc. Le processeur est plutôt lent. Cette lenteur peut être remarquée en écrivant un programme qui imprime 10 000 lignes dans un fichier ligne par ligne, au lieu de les copier dans le tampon et d'enregistrer immédiatement. Le disque dur est connecté au pont sud et à l'intérieur il y a également un contrôleur qui contrôle le placement direct des données.La RAM est connectée au CPU via le bus et sa lecture prend un certain temps. Pour accélérer le CPU, il dispose d'un cache, c'est-à-dire La zone dans laquelle se trouvent les transistors représentant des données qui seront bientôt nécessaires ou souvent utilisées, leur lecture est beaucoup plus rapide que celle de la carte RAM, qui communique avec le CPU via le North Bridge. La RAM est appelée Dynamic Random Access Memory , car les condensateurs sont utilisés pour représenter les données qu'elle contient. Un condensateur est un élément radio qui, comme une batterie, conserve une charge pendant un certain temps jusqu'à ce qu'il soit complètement déchargé. Ce n'est qu'ici que la décharge se produit très rapidement. Par conséquent, les condensateurs doivent être rechargés, cela se produit instantanément, il suffit d'appliquer une tension. Condensateur chargé - logique 1, sinon 0. Pour la mémoire cache est utiliséeRAM statique, c'est-à-dire il n'a pas besoin d'être rechargé et fonctionne donc plus rapidement, mais coûte plus cher. Le cache est divisé en 3 niveaux, qui sont vérifiés séquentiellement lors de la recherche des données demandées avant que le processeur n'accède à la RAM. Sur les processeurs plus anciens, le cache de premier niveau (L1) faisait partie du processeur et fonctionnait avec lui à la même fréquence, lorsque les caches L2 et L3 étaient des puces externes. Maintenant, ils sont tous sur la même puce que le processeur. Le cache L1 est le plus rapide et le plus petit en taille de mémoire, L2 a plus de mémoire mais plus lentement. L3 est le plus grand cache et le plus lent, souvent appelé cache partagé , car il stocke les données pour tous les cœurs de processeur, tandis que L1 et L2 sont créés pour chaque cœur individuel.Dans la partie suivante, nous parlerons de la façon dont Windows reçoit et traite les données reçues.