El nuevo laboratorio de Síntesis Digital continúa la tradición del tutorial de David Harris y Sarah Harris, Digital Circuitry and Computer Architecture, que descargó el sitio británico . El laboratorio le permite tocar toda la teoría de Harris & Harris en la placa FPGA, desde las luces intermitentes hasta el procesador. El concepto de procesamiento del transportador también se analiza en el laboratorio, sin el cual no pasará una entrevista para trabajar como diseñador en ninguna empresa de microelectrónica. Al final, el camino de FPGA a ASIC, circuitos de masa que están en iPhones, Tesla y aceleradores de IA.El libro contiene una entrevista con un equipo de San Petersburgo que Intel trajo a su sede en Silicon Valley para su victoria en el concurso Innovate FPGA. Libro "Síntesis digital: un curso práctico"Cadence Design Systems, una compañía líder en la automatización del diseño de microcircuitos, es compatible (en la foto de arriba, Siberian Natasha está parada con una placa FPGA frente a la sede de Cadence en Silicon Valley; su video estará en la publicación).Labnik fue creado bajo los auspicios de la Escuela Superior de Economía / MIEM (Alexander Romanov, Veronika Prokhorova e Igor Agamirzyan), mientras que los maestros de las universidades de Moscú, Kiev y Samara, San Petersburgo ITMO, Chernihiv Polytechnic y la Universidad de California Santa Cruz ( Charles Danchek , en inglés) escribieron diferentes capítulos . oficina vespertina en Silicon Valley). A la creación del libro de texto asistieron ingenieros de la compañía rusa IVA Technologies (Stanislav Zhelnio, acelerador de hardware AI + proyecto educativo schoolMIPS) y FSUE NPTSAP(departamento de Roscosmos), empresas estadounidenses MIPS, Juniper Networks y AMD. Publicó un libro de texto DMK-Press.Elaboré un plan para el laboratorio y atraje a autores de proyectos educativos anteriores, después de lo cual transferí el control a Alexander Romanov, quien realizó un trabajo minucioso y administró el proyecto durante casi dos años. La creación del libro de texto encaja naturalmente en las actividades de Alexander , quien durante 3 años crió el laboratorio en el HSE MIEM , que se ocupa de computadoras integradas, robótica y FPGA. El laboratorio organizó varios equipos en Innovate FPGA, uno de los cuales se convirtió en medallista de bronce en las finales regionales.El libro de texto no solo es adecuado para estudiantes, sino que también se puede usar para campamentos de verano de diseño digital para estudiantes avanzados. Comprender los tutoriales en Internet desde cero sobre cómo trabajar con el entorno Intel Quartus II no es trivial. Y en el libro de texto todo se describe en pasos. Además, tiene toda la base teórica para hacer algo interesante para los escolares, además de luces intermitentes que los molestan rápidamente. Interesante es, por ejemplo, un videojuego:

El nuevo laboratorio de Síntesis Digital continúa la tradición del tutorial de David Harris y Sarah Harris, Digital Circuitry and Computer Architecture, que descargó el sitio británico . El laboratorio le permite tocar toda la teoría de Harris & Harris en la placa FPGA, desde las luces intermitentes hasta el procesador. El concepto de procesamiento del transportador también se analiza en el laboratorio, sin el cual no pasará una entrevista para trabajar como diseñador en ninguna empresa de microelectrónica. Al final, el camino de FPGA a ASIC, circuitos de masa que están en iPhones, Tesla y aceleradores de IA.El libro contiene una entrevista con un equipo de San Petersburgo que Intel trajo a su sede en Silicon Valley para su victoria en el concurso Innovate FPGA. Libro "Síntesis digital: un curso práctico"Cadence Design Systems, una compañía líder en la automatización del diseño de microcircuitos, es compatible (en la foto de arriba, Siberian Natasha está parada con una placa FPGA frente a la sede de Cadence en Silicon Valley; su video estará en la publicación).Labnik fue creado bajo los auspicios de la Escuela Superior de Economía / MIEM (Alexander Romanov, Veronika Prokhorova e Igor Agamirzyan), mientras que los maestros de las universidades de Moscú, Kiev y Samara, San Petersburgo ITMO, Chernihiv Polytechnic y la Universidad de California Santa Cruz ( Charles Danchek , en inglés) escribieron diferentes capítulos . oficina vespertina en Silicon Valley). A la creación del libro de texto asistieron ingenieros de la compañía rusa IVA Technologies (Stanislav Zhelnio, acelerador de hardware AI + proyecto educativo schoolMIPS) y FSUE NPTSAP(departamento de Roscosmos), empresas estadounidenses MIPS, Juniper Networks y AMD. Publicó un libro de texto DMK-Press.Elaboré un plan para el laboratorio y atraje a autores de proyectos educativos anteriores, después de lo cual transferí el control a Alexander Romanov, quien realizó un trabajo minucioso y administró el proyecto durante casi dos años. La creación del libro de texto encaja naturalmente en las actividades de Alexander , quien durante 3 años crió el laboratorio en el HSE MIEM , que se ocupa de computadoras integradas, robótica y FPGA. El laboratorio organizó varios equipos en Innovate FPGA, uno de los cuales se convirtió en medallista de bronce en las finales regionales.El libro de texto no solo es adecuado para estudiantes, sino que también se puede usar para campamentos de verano de diseño digital para estudiantes avanzados. Comprender los tutoriales en Internet desde cero sobre cómo trabajar con el entorno Intel Quartus II no es trivial. Y en el libro de texto todo se describe en pasos. Además, tiene toda la base teórica para hacer algo interesante para los escolares, además de luces intermitentes que los molestan rápidamente. Interesante es, por ejemplo, un videojuego: La idea de aprender Verilo a través de los juegos VGA no es nueva: muchas universidades tienen dicho laboratorio, por ejemplo, en el Instituto de Tecnología de Massachusetts (MIT) 6.111 Laboratorio Introductorio de Sistemas Digitales. Además, hace dos años, se publicó el libro Designing Video Game Hardware in Verilog Paperback de Steven Hugg, con juegos bastante desarrollados con tanques, autos de carrera, un generador de cielo estrellado pseudoaleatorio usando LFSR, un buffer de cuadro e incluso una interfaz de hardware y software. Además, los juegos VGA están en demostraciones de fabricantes de FPGA Xilinx e Intel / Altera, más precisamente de sus compañías asociadas: Digilent y Terasic.

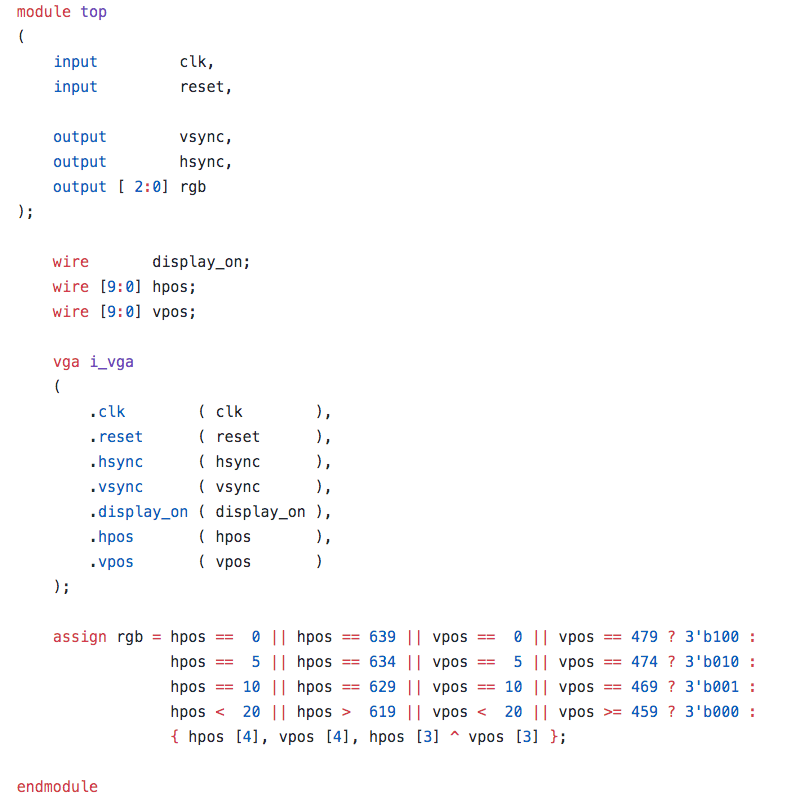

La idea de aprender Verilo a través de los juegos VGA no es nueva: muchas universidades tienen dicho laboratorio, por ejemplo, en el Instituto de Tecnología de Massachusetts (MIT) 6.111 Laboratorio Introductorio de Sistemas Digitales. Además, hace dos años, se publicó el libro Designing Video Game Hardware in Verilog Paperback de Steven Hugg, con juegos bastante desarrollados con tanques, autos de carrera, un generador de cielo estrellado pseudoaleatorio usando LFSR, un buffer de cuadro e incluso una interfaz de hardware y software. Además, los juegos VGA están en demostraciones de fabricantes de FPGA Xilinx e Intel / Altera, más precisamente de sus compañías asociadas: Digilent y Terasic. En particular, en el laboratorio del MITse muestra muy claramente que todo lo que necesita hacer para dibujar en la pantalla es implementar en forma de diagrama una función que tome las coordenadas X e Y de un punto en la pantalla como argumento y devuelva el color de ese punto (RGB). En el caso más simple, esta función es una función combinada, por ejemplo, dicha función dibujará la obra maestra de Malevich: "el color es negro (RGB = 0,0,0) si x> = 200 y x <= 400 e y> = 200 e y <400, de lo contrario blanco (RGB = 1,1,1) ". Además, llamaremos a dicho circuito un "mezclador", ya que "mezclará" entradas de generadores de diferentes imágenes.Para generar los argumentos del mezclador X e Y, se usa un circuito simple de dos contadores que usa la señal de reloj de alta frecuencia CLK. Además de las coordenadas X e Y, este circuito también genera señales HSYNC y VSYNC para la pantalla VGA. Las señales HSYNC y VSYNC han permanecido desde la época del tubo de rayos catódicos. Le dicen al haz virtual cuándo moverse al siguiente punto / píxel en la pantalla horizontalmente, y luego a la siguiente fila verticalmente.En un caso difícil, el mezclador usa no solo los valores de sus entradas X e Y, sino también los valores de los elementos de estado (D-flip-flops y memoria), que se registran utilizando la señal de reloj CLK. En este caso, el reloj también ingresa al mezclador. Los circuitos con señales de reloj y elementos de estado se denominan secuenciales (estos circuitos pasan por una secuencia de estados que pulsa claramente una señal de reloj pulsante). En mezcladores secuenciales, puede implementar imágenes en movimiento de cualquier grado de complejidad.Aquí están las imágenes del laboratorio de shnaya del MIT (el mismo está en el montón de otras universidades), ilustrando la función del generador HSYNC / VSYNC, el mezclador (de la misma unidad que calcula RGB como una función de X / HCOUNT e Y / VCOUNT), así como la salida de HSYNC, VSYNC y RGB en la pantalla. La imagen usa un interruptor / multiplexor entre tres mezcladores: uno dibuja rayas, otro dibuja un rectángulo y el tercero dibuja una imagen en la pantalla mientras juega ping pong:

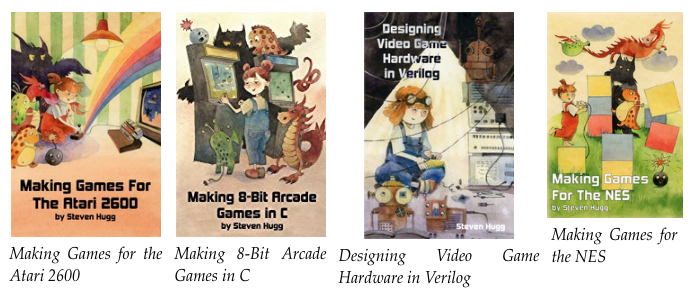

En particular, en el laboratorio del MITse muestra muy claramente que todo lo que necesita hacer para dibujar en la pantalla es implementar en forma de diagrama una función que tome las coordenadas X e Y de un punto en la pantalla como argumento y devuelva el color de ese punto (RGB). En el caso más simple, esta función es una función combinada, por ejemplo, dicha función dibujará la obra maestra de Malevich: "el color es negro (RGB = 0,0,0) si x> = 200 y x <= 400 e y> = 200 e y <400, de lo contrario blanco (RGB = 1,1,1) ". Además, llamaremos a dicho circuito un "mezclador", ya que "mezclará" entradas de generadores de diferentes imágenes.Para generar los argumentos del mezclador X e Y, se usa un circuito simple de dos contadores que usa la señal de reloj de alta frecuencia CLK. Además de las coordenadas X e Y, este circuito también genera señales HSYNC y VSYNC para la pantalla VGA. Las señales HSYNC y VSYNC han permanecido desde la época del tubo de rayos catódicos. Le dicen al haz virtual cuándo moverse al siguiente punto / píxel en la pantalla horizontalmente, y luego a la siguiente fila verticalmente.En un caso difícil, el mezclador usa no solo los valores de sus entradas X e Y, sino también los valores de los elementos de estado (D-flip-flops y memoria), que se registran utilizando la señal de reloj CLK. En este caso, el reloj también ingresa al mezclador. Los circuitos con señales de reloj y elementos de estado se denominan secuenciales (estos circuitos pasan por una secuencia de estados que pulsa claramente una señal de reloj pulsante). En mezcladores secuenciales, puede implementar imágenes en movimiento de cualquier grado de complejidad.Aquí están las imágenes del laboratorio de shnaya del MIT (el mismo está en el montón de otras universidades), ilustrando la función del generador HSYNC / VSYNC, el mezclador (de la misma unidad que calcula RGB como una función de X / HCOUNT e Y / VCOUNT), así como la salida de HSYNC, VSYNC y RGB en la pantalla. La imagen usa un interruptor / multiplexor entre tres mezcladores: uno dibuja rayas, otro dibuja un rectángulo y el tercero dibuja una imagen en la pantalla mientras juega ping pong: en el código, el mezclador más simple se ve así. Dibuja cuadrados multicolores a partir de mezclas de rojo, azul y verde, así como líneas de colores puros: de

en el código, el mezclador más simple se ve así. Dibuja cuadrados multicolores a partir de mezclas de rojo, azul y verde, así como líneas de colores puros: de esta manera, puede dibujar una variedad de coloridas imágenes estáticas. Aquí están las imágenes que los estudiantes pintaron en una escuela de verano en Zelenograd inmediatamente después de una breve conferencia explicando cómo hacerlo:

esta manera, puede dibujar una variedad de coloridas imágenes estáticas. Aquí están las imágenes que los estudiantes pintaron en una escuela de verano en Zelenograd inmediatamente después de una breve conferencia explicando cómo hacerlo: Bueno, los escolares pueden codificar la función RGB (X, Y) y dibujar imágenes estáticas. Pero qué hacer a continuación, ¿cuál es el siguiente paso? Examinamos la posibilidad de usar materiales de MIT, Digilent + Xilinx, Altera + Terasic y Steven Hugg, después de lo cual llegamos a la conclusión de que no se pueden usar en su forma pura. Los laboratorios universitarios están incluidos en el programa universitario, y los materiales de los vendedores de FPGA no están bien escritos, y tampoco contienen consejos sobre cómo cambiar el código en el formato de una escuela de verano para que los estudiantes inventen sus juegos. El libro de Stephen Hugg tiene dos inconvenientes que son la otra cara de sus virtudes (vivacidad y colorido):En general, el verilog de Stephen Hugg está a la par con la programación de los procesadores de las antiguas consolas de 8 bits de Atari y Nintendo. Por lo tanto, Hugg no se enfoca en capacitar a futuros superdiseñadores, sino en nostalgianos, informáticos retro y otros recreadores. La diferencia entre su entorno y las herramientas de diseño profesional es aún mayor que entre el entorno de programación Arduino y los kits de herramientas para STM32.

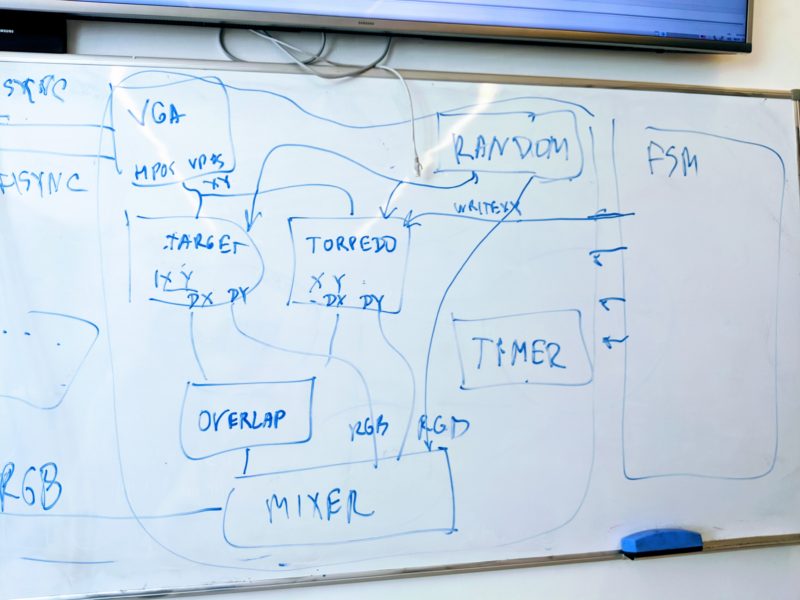

Bueno, los escolares pueden codificar la función RGB (X, Y) y dibujar imágenes estáticas. Pero qué hacer a continuación, ¿cuál es el siguiente paso? Examinamos la posibilidad de usar materiales de MIT, Digilent + Xilinx, Altera + Terasic y Steven Hugg, después de lo cual llegamos a la conclusión de que no se pueden usar en su forma pura. Los laboratorios universitarios están incluidos en el programa universitario, y los materiales de los vendedores de FPGA no están bien escritos, y tampoco contienen consejos sobre cómo cambiar el código en el formato de una escuela de verano para que los estudiantes inventen sus juegos. El libro de Stephen Hugg tiene dos inconvenientes que son la otra cara de sus virtudes (vivacidad y colorido):En general, el verilog de Stephen Hugg está a la par con la programación de los procesadores de las antiguas consolas de 8 bits de Atari y Nintendo. Por lo tanto, Hugg no se enfoca en capacitar a futuros superdiseñadores, sino en nostalgianos, informáticos retro y otros recreadores. La diferencia entre su entorno y las herramientas de diseño profesional es aún mayor que entre el entorno de programación Arduino y los kits de herramientas para STM32. Por supuesto, no propongo culpar a Cadence SimVision y Synopsys Design Compiler por cientos de miles de dólares a los escolares, pero los escolares pueden obtener versiones gratuitas de herramientas profesionales Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, así como Icarus Verilog, GTKWave y el edaplayground en línea . com .Volví a leer el párrafo anterior y pensé: pero Cadence SimVision para la escuela de verano en Zelenograd podría haberse usado. Se hace mejor y más conveniente, tanto su competidor directo Synopsys Design Vision Environment (DVE) * , como los fondos de Mentor Graphics (ModelSim gratuito y Questa pagado), y todas las herramientas baratas y gratuitas (IcarusVerilog, etc.) si la sucursal de Cadence en Moscú El Sistema de Diseño nos dará el derecho y el apoyo para usar su software en las escuelas de verano en Zelenograd, personalmente lo haré por integrar esto en el plan de estudios de la escuela.* Para DVE, por ejemplo, el texto en la ventana de origen tiene errores / saltos cuando lo ejecuto en Ubuntu. Tengo que cambiar el tamaño de la ventana hasta que deje de fallar. SimVision no tiene esto.Aquí está el comienzo del tutorial de SimVision (22 videos en total):Pero volvamos a los juegos. Si no es Stephen Hugg, ¿entonces qué? Escribí un ejemplo de un juego simple que usé en una escuela de verano en Zelenograd . Las fuentes del juego están en el github . Se parece a esto:Durante dos semanas, los estudiantes descubrieron los principios básicos de diseño a nivel de transferencias de registros y comenzaron a hacer sus propios juegos, y no triviales:Hablemos de los detalles técnicos de un juego de ejemplo. Un módulo de juego independiente de la plataforma se puede colocar (instanciar) en el contenedor de cualquier placa FPGA que tenga un puerto VGA y dos botones. Si la placa está completamente vacía, puede conectarle un adaptador para VGA y botones a través de los cables GPIO (entrada / salida de propósito general). El módulo del juego consta de:

Por supuesto, no propongo culpar a Cadence SimVision y Synopsys Design Compiler por cientos de miles de dólares a los escolares, pero los escolares pueden obtener versiones gratuitas de herramientas profesionales Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, así como Icarus Verilog, GTKWave y el edaplayground en línea . com .Volví a leer el párrafo anterior y pensé: pero Cadence SimVision para la escuela de verano en Zelenograd podría haberse usado. Se hace mejor y más conveniente, tanto su competidor directo Synopsys Design Vision Environment (DVE) * , como los fondos de Mentor Graphics (ModelSim gratuito y Questa pagado), y todas las herramientas baratas y gratuitas (IcarusVerilog, etc.) si la sucursal de Cadence en Moscú El Sistema de Diseño nos dará el derecho y el apoyo para usar su software en las escuelas de verano en Zelenograd, personalmente lo haré por integrar esto en el plan de estudios de la escuela.* Para DVE, por ejemplo, el texto en la ventana de origen tiene errores / saltos cuando lo ejecuto en Ubuntu. Tengo que cambiar el tamaño de la ventana hasta que deje de fallar. SimVision no tiene esto.Aquí está el comienzo del tutorial de SimVision (22 videos en total):Pero volvamos a los juegos. Si no es Stephen Hugg, ¿entonces qué? Escribí un ejemplo de un juego simple que usé en una escuela de verano en Zelenograd . Las fuentes del juego están en el github . Se parece a esto:Durante dos semanas, los estudiantes descubrieron los principios básicos de diseño a nivel de transferencias de registros y comenzaron a hacer sus propios juegos, y no triviales:Hablemos de los detalles técnicos de un juego de ejemplo. Un módulo de juego independiente de la plataforma se puede colocar (instanciar) en el contenedor de cualquier placa FPGA que tenga un puerto VGA y dos botones. Si la placa está completamente vacía, puede conectarle un adaptador para VGA y botones a través de los cables GPIO (entrada / salida de propósito general). El módulo del juego consta de:- Generador de escaneo VGA.

- Dos módulos de trabajo paralelos para torpedos de sprites y objetivos de sprites.

- La máquina de estados para el escenario del juego, con los estados "inicio", "orientación", "moscas", "victoria / derrota".

- Un módulo que determina si los sprites colisionaron.

- Un temporizador para establecer la duración del efecto visual después de ganar (pantalla de frambuesa parpadeante) o derrota (pantalla amarilla).

Para la próxima escuela, todas estas imágenes deben volver a dibujarse usando draw.io o Lucidchart en diagramas de microarquitectura normales:

Para la próxima escuela, todas estas imágenes deben volver a dibujarse usando draw.io o Lucidchart en diagramas de microarquitectura normales: también debe agregar a los materiales de la escuela diagramas de tiempo dibujados usando WaveDrom para mostrar cómo funciona el generador de escaneo VGA, así como cómo la mini tubería calcula las coordenadas ruta de datos dentro de sprites:

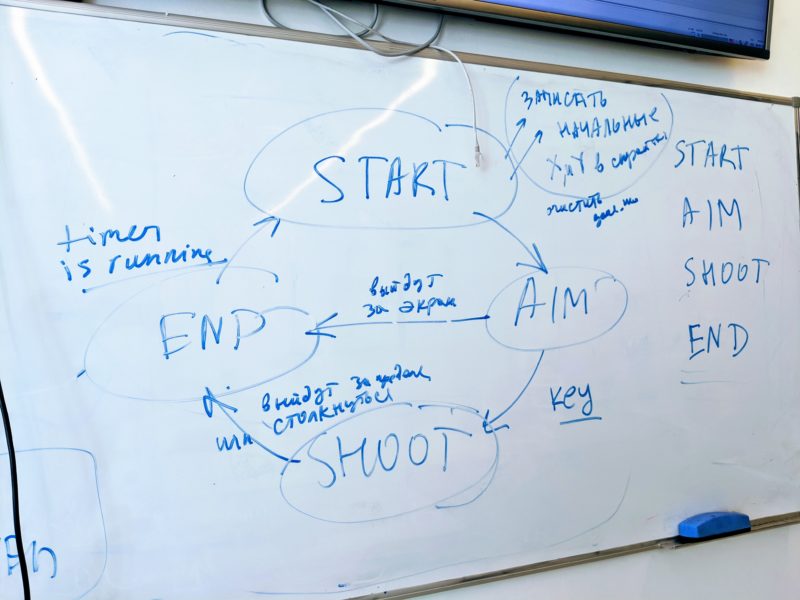

también debe agregar a los materiales de la escuela diagramas de tiempo dibujados usando WaveDrom para mostrar cómo funciona el generador de escaneo VGA, así como cómo la mini tubería calcula las coordenadas ruta de datos dentro de sprites: Y, por supuesto, debe dibujar diagramas de la máquina de estados finitos. Hice una docena de variantes de la máquina de estados finitos de este juego, aquí en el tablero hay una variante con cuatro estados:

Y, por supuesto, debe dibujar diagramas de la máquina de estados finitos. Hice una docena de variantes de la máquina de estados finitos de este juego, aquí en el tablero hay una variante con cuatro estados: ¿Por qué tomé muchas decisiones? Incluso con una máquina tan simple, puede comparar diferentes estilos de su codificación en un veril, así como ilustrar la optimización de estados y tiempos. Todo esto se pide en una entrevista para un puesto como diseñador de chips en Apple, NVidia, Intel, AMD y otras compañías. Por lo tanto, esta área debe ser conocida para que los dientes reboten. Hay algunos buenos artículos de Clifford Cummings sobre este tema:

¿Por qué tomé muchas decisiones? Incluso con una máquina tan simple, puede comparar diferentes estilos de su codificación en un veril, así como ilustrar la optimización de estados y tiempos. Todo esto se pide en una entrevista para un puesto como diseñador de chips en Apple, NVidia, Intel, AMD y otras compañías. Por lo tanto, esta área debe ser conocida para que los dientes reboten. Hay algunos buenos artículos de Clifford Cummings sobre este tema:- Artículo más nuevo de 2019: Diseño y síntesis FiniteStateMachine (FSM) usando SystemVerilog - Parte I por Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

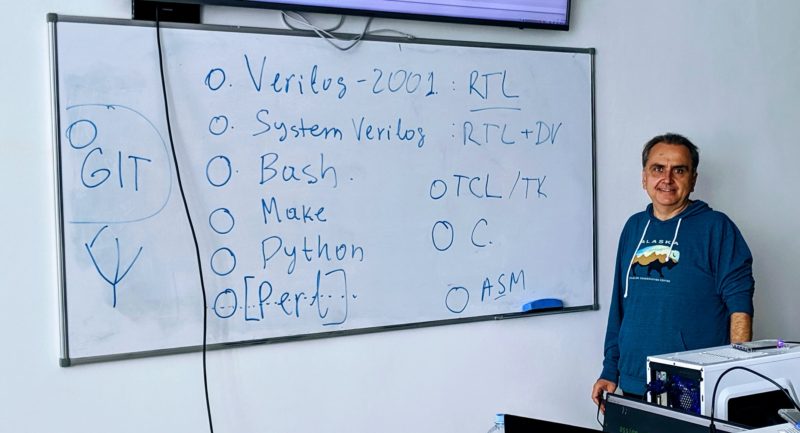

Sinteticé varias versiones de la máquina de estado del juego usando la herramienta de compilación de diseño Synopsys más popular en la industria e hice una tableta de este tipo. Como podemos ver, la versión moderna de DC optimiza todos los estilos de manera muy eficiente, por lo que es posible extraer picosegundos en las máquinas de estado, pero no es necesario. Aunque es posible para máquinas de estado finito más complejas, los trucos de los artículos de Cummings serán más críticos: durante la escuela en Zelenograd, también discutimos que en el diseño de chips, además de los lenguajes de descripción de hardware Verilog y VHDL, se usan muchos lenguajes auxiliares:

durante la escuela en Zelenograd, también discutimos que en el diseño de chips, además de los lenguajes de descripción de hardware Verilog y VHDL, se usan muchos lenguajes auxiliares:Python se utiliza para automatizar el ensamblaje, la gestión de regresión y extraer información de informes de síntesis y generación de código, así como bash, make y otras cocinas Unix / Linux.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ y bibliotecas como SystemC se utilizan para escribir modelos de bloques de hardware a nivel de transacción. Los ingenieros de verificación comprueban los bloques diseñados en el veril con estos modelos.

Si trabaja para una empresa de procesadores, es bueno que conozca al ensamblador. Incluso si no es un programador de bajo nivel y no un verificador, sino un diseñador de procesadores a nivel de transferencias de registro (Nivel de transferencia de registro - RTL).

Aquí hay enlaces para aquellos interesados en usar pearl como preprocesador para verilogue:- G. Spivey. EP3: un preprocesador de Perl extensible

- Página de manual de vpp.pl

- Un preprocesador Verilog

Un ejemplo de cómo usar la perla de registro integrada para conectar 64 puertos://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Sería bueno que alguien escribiera scripts universales para modelar y sintetizar un ejemplo (no necesariamente mi juego) en todas las plataformas principales para síntesis, simulación, depuración, análisis de consumo dinámico de energía, diseño físico, encuadernación para todos los tableros, etc. Esto podría usarse en escuelas y seminarios:

Sería bueno que alguien escribiera scripts universales para modelar y sintetizar un ejemplo (no necesariamente mi juego) en todas las plataformas principales para síntesis, simulación, depuración, análisis de consumo dinámico de energía, diseño físico, encuadernación para todos los tableros, etc. Esto podría usarse en escuelas y seminarios: Aquí puede tener una pregunta: ¿por qué uso seminarios de Linux? Aunque Windows también tiene un entorno de modelado y síntesis para FPGA, Windows no se ha arraigado en la industria del diseño de chips masivos. A principios de la década de 1990, el mercado de estaciones de trabajo para desarrolladores ASIC se dividió entre SunOS y HP / UX. Luego, las compañías electrónicas jugaron durante tres años con Windows NT, pero no funcionó. Después de eso, Synopsys y otras compañías de software de diseño escupieron y cambiaron a Linux, primero en Red Hat, luego en SuSE y Ubuntu. Sospecho, principalmente debido a un montón de scripts en el pearl, C-shell, etc., así como por el trabajo remoto de los desarrolladores a través de telnet y X Window.Por lo tanto, para mis seminarios voy con un montón de SSD de arranque con Lubuntu, en el que está instalado todo el software necesario. Utilizo el arranque heredado, pero recientemente resultó que cada vez más computadoras requieren el arranque UEFI. Aparentemente, necesitará hacer un SSD de arranque con arranque UEFI.Las compañías de rápido movimiento usan CentOS en lugar de Red Hat. Quizás muchas herramientas de diseño están bajo Debian, pero no lo he probado.

Aquí puede tener una pregunta: ¿por qué uso seminarios de Linux? Aunque Windows también tiene un entorno de modelado y síntesis para FPGA, Windows no se ha arraigado en la industria del diseño de chips masivos. A principios de la década de 1990, el mercado de estaciones de trabajo para desarrolladores ASIC se dividió entre SunOS y HP / UX. Luego, las compañías electrónicas jugaron durante tres años con Windows NT, pero no funcionó. Después de eso, Synopsys y otras compañías de software de diseño escupieron y cambiaron a Linux, primero en Red Hat, luego en SuSE y Ubuntu. Sospecho, principalmente debido a un montón de scripts en el pearl, C-shell, etc., así como por el trabajo remoto de los desarrolladores a través de telnet y X Window.Por lo tanto, para mis seminarios voy con un montón de SSD de arranque con Lubuntu, en el que está instalado todo el software necesario. Utilizo el arranque heredado, pero recientemente resultó que cada vez más computadoras requieren el arranque UEFI. Aparentemente, necesitará hacer un SSD de arranque con arranque UEFI.Las compañías de rápido movimiento usan CentOS en lugar de Red Hat. Quizás muchas herramientas de diseño están bajo Debian, pero no lo he probado. Para los seminarios, utilizo tableros de FPGA chinos, uno de los cuales está en mis manos por una niña de Novosibirsk, Natasha, que organiza fiestas What-Where-When en nuestro Silicon Valley .

Para los seminarios, utilizo tableros de FPGA chinos, uno de los cuales está en mis manos por una niña de Novosibirsk, Natasha, que organiza fiestas What-Where-When en nuestro Silicon Valley . En el mes de marzo, caminé por la vida salvaje de California junto con el empresario ruso Sergei Zorin., que llevó una docena de tablas de ZEOWAA a Moscú, de características similares a las que Natasha tiene en sus manos.Dado que probablemente no habrá seminarios en Zelenograd debido al coronavirus este verano, creo que daré esta docena de tarifas a los escolares de Moscú de forma gratuita (UPD: los escolares de otras ciudades también pueden hacerlo, aunque existe un alboroto adicional con el reenvío). Con dos condiciones:

En el mes de marzo, caminé por la vida salvaje de California junto con el empresario ruso Sergei Zorin., que llevó una docena de tablas de ZEOWAA a Moscú, de características similares a las que Natasha tiene en sus manos.Dado que probablemente no habrá seminarios en Zelenograd debido al coronavirus este verano, creo que daré esta docena de tarifas a los escolares de Moscú de forma gratuita (UPD: los escolares de otras ciudades también pueden hacerlo, aunque existe un alboroto adicional con el reenvío). Con dos condiciones:Antes de obtener una placa, debe pasar por las tres partes del curso en línea "Cómo funcionan los creadores de nanochips inteligentes" ( "Del transistor al microcircuito" , "El lado lógico de los circuitos digitales" , "El lado físico de los circuitos digitales" ) y obtener un certificado. Creamos este curso junto con RUSNANO, o más bien, su hija educativa eNano, el proyecto STEMford.

, , , . , , , ( ) . , , .

, , .

Si desea comprar un nuevo libro "Síntesis lógica" como ayuda para tal proyecto , entonces para los lectores de Habr tiene un código promocional: Sintez_2020. En el futuro, sería bueno dejar de usar tablas chinas y hacer una tabla rusa barata para tales ejercicios con FPGA, con un diseño abierto. Le doy la bienvenida si comparte sus pensamientos en los comentarios sobre el software de diseño de la placa e ideas sobre cómo diseñar y comercializar mejor dicha placa. Para uso masivo con escolares, es deseable que no cueste más de $ 30 o 2000 rublos.

En el futuro, sería bueno dejar de usar tablas chinas y hacer una tabla rusa barata para tales ejercicios con FPGA, con un diseño abierto. Le doy la bienvenida si comparte sus pensamientos en los comentarios sobre el software de diseño de la placa e ideas sobre cómo diseñar y comercializar mejor dicha placa. Para uso masivo con escolares, es deseable que no cueste más de $ 30 o 2000 rublos. Si eres estudiante y estás interesado en el diseño de microcircuitos, puedes ir a MIET, HSE MIEM, el Instituto de Física de Ingeniería de Moscú, la Universidad Estatal de Moscú, el Instituto de Física y Tecnología de Moscú ( Nikita Polyakov participa en dichos ejercicios, MPEI, MISiS, ITMO, LETI, Universidad de Samara, algunas universidades ucranianas (KNU, Chernihiv NTU, Kharkov KNURE) y otras universidades. Así que descubrí cómo se estaba reparando mi enfoque al comité de selección de MIET en Zelenograd: así

Si eres estudiante y estás interesado en el diseño de microcircuitos, puedes ir a MIET, HSE MIEM, el Instituto de Física de Ingeniería de Moscú, la Universidad Estatal de Moscú, el Instituto de Física y Tecnología de Moscú ( Nikita Polyakov participa en dichos ejercicios, MPEI, MISiS, ITMO, LETI, Universidad de Samara, algunas universidades ucranianas (KNU, Chernihiv NTU, Kharkov KNURE) y otras universidades. Así que descubrí cómo se estaba reparando mi enfoque al comité de selección de MIET en Zelenograd: así es como se ve MIET en el interior: puede

es como se ve MIET en el interior: puede encontrar un trabajo justo enfrente de MIET para la ONG ELVIS, que se ocupa de cámaras inteligentes y chips para satélites:

encontrar un trabajo justo enfrente de MIET para la ONG ELVIS, que se ocupa de cámaras inteligentes y chips para satélites: O puede venir a Silicon Valley. ¿Quieres tener una entrevista con Dolina? ¡Practica en tableros FPGA!

O puede venir a Silicon Valley. ¿Quieres tener una entrevista con Dolina? ¡Practica en tableros FPGA!