The new Digital Synthesis lab continues the tradition of David Harris and Sarah Harris's tutorial, Digital Circuitry and Computer Architecture, which downloaded the British site . The lab allows you to touch the entire theory of Harris & Harris on the FPGA board, from flashing lights to the processor. The concept of conveyor processing is also analyzed in the lab, without which you will not pass an interview to work as a designer in any microelectronic company. At the end, the path from FPGA to ASIC, mass circuits that are in iPhones, Tesla and AI accelerators.The book contains an interview with a team from St. Petersburg that Intel brought to its headquarters in Silicon Valley for their victory in the Innovate FPGA contest. Book "Digital Synthesis: A Practical Course"Cadence Design Systems, a leading company in the automation of microcircuit design, supported (in the photo above, Siberian Natasha is standing with an FPGA board in front of Cadence headquarters in Silicon Valley - her video will be in the post).Labnik was created under the auspices of the Higher School of Economics / MIEM (Alexander Romanov, Veronika Prokhorova and Igor Agamirzyan), while different chapters were written by teachers from Moscow, Kiev and Samara Universities, St. Petersburg ITMO, Chernihiv Polytechnic, and the University of California Santa Cruz ( Charles Danchek , evening office in Silicon Valley). The creation of the textbook was attended by engineers of the Russian company IVA Technologies (Stanislav Zhelnio, hardware accelerator AI + educational project schoolMIPS) and FSUE NPTSAP(department of Roscosmos), American companies MIPS, Juniper Networks and AMD. Published a textbook DMK-Press.I drew up a plan for the lab and attracted authors from previous educational projects, after which I transferred control to Alexander Romanov, who carried out painstaking work, managing the project for almost two years. The creation of the textbook naturally fit into the activities of Alexander , who for 3 years raised the laboratory at the HSE MIEM , which deals with embedded computers, robotics and FPGAs. The lab organized several teams at the Innovate FPGA, one of which became a bronze medalist in the regional finals.The textbook is not only suitable for students - it can be used for digital design summer camps for advanced students. Understanding tutorials on the Internet from scratch on how to work with the Intel Quartus II environment is not trivial. And in the textbook it is all described in steps. In addition, it has all the theoretical basis to do something interesting for schoolchildren, in addition to flashing lights that quickly bother them. Interesting is for example a video game:

The new Digital Synthesis lab continues the tradition of David Harris and Sarah Harris's tutorial, Digital Circuitry and Computer Architecture, which downloaded the British site . The lab allows you to touch the entire theory of Harris & Harris on the FPGA board, from flashing lights to the processor. The concept of conveyor processing is also analyzed in the lab, without which you will not pass an interview to work as a designer in any microelectronic company. At the end, the path from FPGA to ASIC, mass circuits that are in iPhones, Tesla and AI accelerators.The book contains an interview with a team from St. Petersburg that Intel brought to its headquarters in Silicon Valley for their victory in the Innovate FPGA contest. Book "Digital Synthesis: A Practical Course"Cadence Design Systems, a leading company in the automation of microcircuit design, supported (in the photo above, Siberian Natasha is standing with an FPGA board in front of Cadence headquarters in Silicon Valley - her video will be in the post).Labnik was created under the auspices of the Higher School of Economics / MIEM (Alexander Romanov, Veronika Prokhorova and Igor Agamirzyan), while different chapters were written by teachers from Moscow, Kiev and Samara Universities, St. Petersburg ITMO, Chernihiv Polytechnic, and the University of California Santa Cruz ( Charles Danchek , evening office in Silicon Valley). The creation of the textbook was attended by engineers of the Russian company IVA Technologies (Stanislav Zhelnio, hardware accelerator AI + educational project schoolMIPS) and FSUE NPTSAP(department of Roscosmos), American companies MIPS, Juniper Networks and AMD. Published a textbook DMK-Press.I drew up a plan for the lab and attracted authors from previous educational projects, after which I transferred control to Alexander Romanov, who carried out painstaking work, managing the project for almost two years. The creation of the textbook naturally fit into the activities of Alexander , who for 3 years raised the laboratory at the HSE MIEM , which deals with embedded computers, robotics and FPGAs. The lab organized several teams at the Innovate FPGA, one of which became a bronze medalist in the regional finals.The textbook is not only suitable for students - it can be used for digital design summer camps for advanced students. Understanding tutorials on the Internet from scratch on how to work with the Intel Quartus II environment is not trivial. And in the textbook it is all described in steps. In addition, it has all the theoretical basis to do something interesting for schoolchildren, in addition to flashing lights that quickly bother them. Interesting is for example a video game: The idea of learning verilo using VGA games is not new - many universities have such a lab, for example, at the 6.111 Introductory Digital Systems Laboratory at the Massachusetts Institute of Technology (MIT). Also, two years ago, the book Designing Video Game Hardware in Verilog Paperback by Steven Hugg was published, with fairly developed games with tanks, race cars, a pseudo-random starry sky generator using LFSR, a frame buffer, and even a hardware-software interface. In addition, VGA games are in demos from manufacturers of FPGAs Xilinx and Intel / Altera, more precisely from their partner companies - Digilent and Terasic.

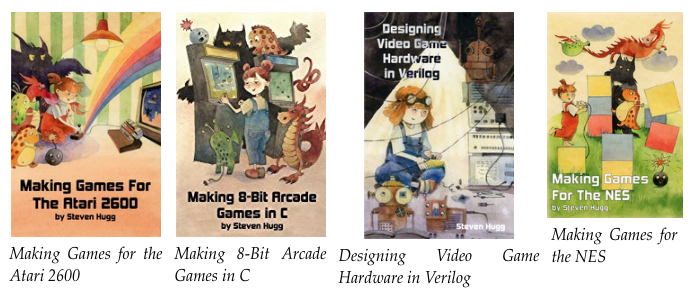

The idea of learning verilo using VGA games is not new - many universities have such a lab, for example, at the 6.111 Introductory Digital Systems Laboratory at the Massachusetts Institute of Technology (MIT). Also, two years ago, the book Designing Video Game Hardware in Verilog Paperback by Steven Hugg was published, with fairly developed games with tanks, race cars, a pseudo-random starry sky generator using LFSR, a frame buffer, and even a hardware-software interface. In addition, VGA games are in demos from manufacturers of FPGAs Xilinx and Intel / Altera, more precisely from their partner companies - Digilent and Terasic. In particular, in the lab from MITit is very clearly shown that all you need to do to draw on the display is to implement in the form of a diagram a function that takes the coordinates X and Y of a point on the screen as an argument and returns the color of that point (RGB). In the simplest case, this function is a combination function, for example, such a function will draw Malevich’s masterpiece: “color is black (RGB = 0,0,0) if x> = 200 and x <= 400 and y> = 200 and y <400, otherwise white (RGB = 1,1,1). " We will further call such a circuit a “mixer”, since it will “mix” inputs from generators of different images.To generate the mixer arguments X and Y themselves, a simple two-counter circuit is used that uses the CLK clock signal. In addition to the X and Y coordinates, this circuit also generates HSYNC and VSYNC signals for the VGA display. The HSYNC and VSYNC signals have remained since the time of the cathode ray tube. They tell the virtual beam when to move to the next point / pixel on the screen horizontally, and then to the next row vertically.In a difficult case, the mixer uses not only the values of its inputs X and Y, but also the values from the state elements (D-flip-flops and memory), which are recorded using the CLK clock signal. In this case, the clock also enters the mixer. Circuits with clock signals and state elements are called sequential (these circuits go through a sequence of states that clearly pulsates a pulsating clock signal). On sequential mixers, you can implement moving images of any degree of complexity.Here are the pictures from the MIT shnaya lab (the same is in the heap of other universities), illustrating the function of the HSYNC / VSYNC generator, the mixer (of the same unit that calculates RGB as a function of X / HCOUNT and Y / VCOUNT), as well as the output of HSYNC, VSYNC and RGB on the screen. The picture uses a switch / multiplexer between three mixers - one draws stripes, another draws a rectangle, and the third draws an image on the screen while playing ping pong:

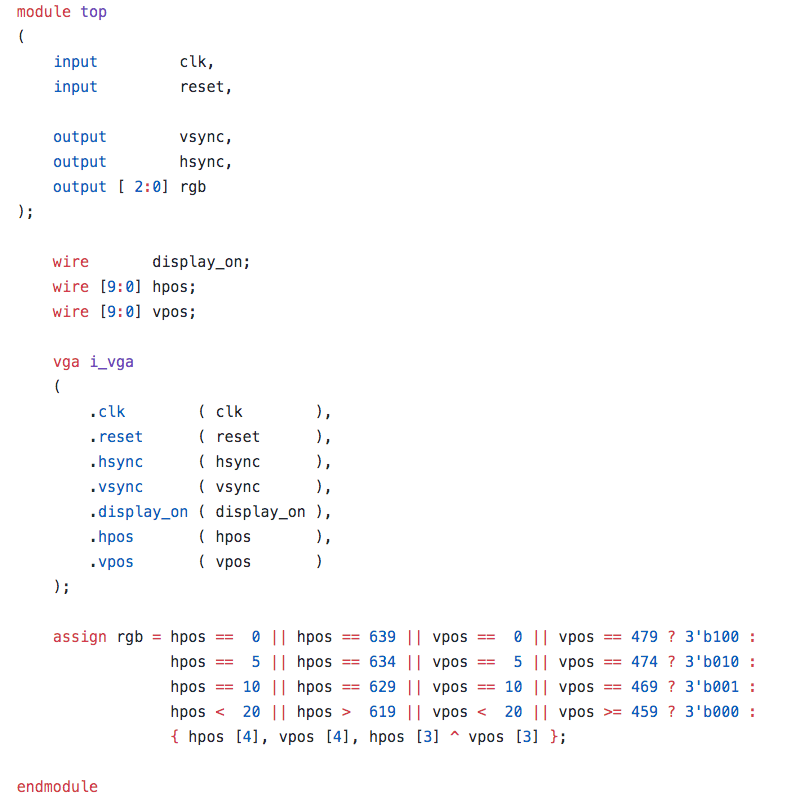

In particular, in the lab from MITit is very clearly shown that all you need to do to draw on the display is to implement in the form of a diagram a function that takes the coordinates X and Y of a point on the screen as an argument and returns the color of that point (RGB). In the simplest case, this function is a combination function, for example, such a function will draw Malevich’s masterpiece: “color is black (RGB = 0,0,0) if x> = 200 and x <= 400 and y> = 200 and y <400, otherwise white (RGB = 1,1,1). " We will further call such a circuit a “mixer”, since it will “mix” inputs from generators of different images.To generate the mixer arguments X and Y themselves, a simple two-counter circuit is used that uses the CLK clock signal. In addition to the X and Y coordinates, this circuit also generates HSYNC and VSYNC signals for the VGA display. The HSYNC and VSYNC signals have remained since the time of the cathode ray tube. They tell the virtual beam when to move to the next point / pixel on the screen horizontally, and then to the next row vertically.In a difficult case, the mixer uses not only the values of its inputs X and Y, but also the values from the state elements (D-flip-flops and memory), which are recorded using the CLK clock signal. In this case, the clock also enters the mixer. Circuits with clock signals and state elements are called sequential (these circuits go through a sequence of states that clearly pulsates a pulsating clock signal). On sequential mixers, you can implement moving images of any degree of complexity.Here are the pictures from the MIT shnaya lab (the same is in the heap of other universities), illustrating the function of the HSYNC / VSYNC generator, the mixer (of the same unit that calculates RGB as a function of X / HCOUNT and Y / VCOUNT), as well as the output of HSYNC, VSYNC and RGB on the screen. The picture uses a switch / multiplexer between three mixers - one draws stripes, another draws a rectangle, and the third draws an image on the screen while playing ping pong: In the code, the simplest mixer looks like this. He draws multi-colored squares from mixtures of red, blue and green, as well as lines of pure colors:

In the code, the simplest mixer looks like this. He draws multi-colored squares from mixtures of red, blue and green, as well as lines of pure colors: In this way, you can draw a variety of colorful static images. Here are the images that students painted at a summer school in Zelenograd immediately after a short lecture explaining how to do it:

In this way, you can draw a variety of colorful static images. Here are the images that students painted at a summer school in Zelenograd immediately after a short lecture explaining how to do it: Well, schoolchildren can encode the RGB (X, Y) function and draw static pictures. But what to do next, what is the next step? We examined the possibility of using materials from MIT, Digilent + Xilinx, Altera + Terasic and Steven Hugg, after which we came to the conclusion that they cannot be used in their pure form. University labs are included in the university program, and materials from FPGA vendors are not well written, and also do not contain tips on how to change the code in the format of a summer school so that students invent their games. The book of Stephen Hugg has two drawbacks that are the flip side of its virtues (liveliness and colorfulness):In general, the verilog at Stephen Hugg stands on a par with the programming of the processors of the old 8-bit consoles from Atari and Nintendo. Thus, Hugg is not focused on training future superdesigners, but on nostalgians, retro computer scientists and other reenactors. The difference between his environment and professional design tools is even greater than between the Arduino programming environment and the toolkits for STM32.

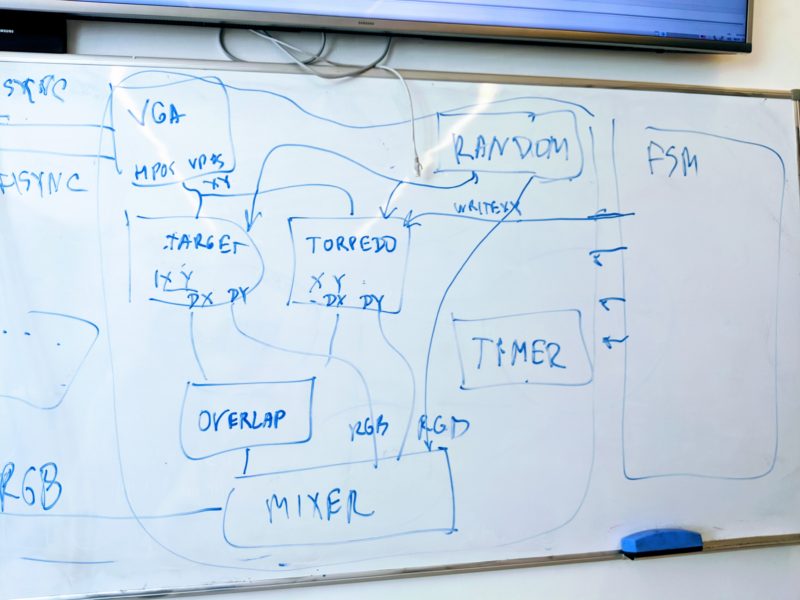

Well, schoolchildren can encode the RGB (X, Y) function and draw static pictures. But what to do next, what is the next step? We examined the possibility of using materials from MIT, Digilent + Xilinx, Altera + Terasic and Steven Hugg, after which we came to the conclusion that they cannot be used in their pure form. University labs are included in the university program, and materials from FPGA vendors are not well written, and also do not contain tips on how to change the code in the format of a summer school so that students invent their games. The book of Stephen Hugg has two drawbacks that are the flip side of its virtues (liveliness and colorfulness):In general, the verilog at Stephen Hugg stands on a par with the programming of the processors of the old 8-bit consoles from Atari and Nintendo. Thus, Hugg is not focused on training future superdesigners, but on nostalgians, retro computer scientists and other reenactors. The difference between his environment and professional design tools is even greater than between the Arduino programming environment and the toolkits for STM32. Of course, I don’t propose to blame Cadence SimVision and Synopsys Design Compiler for schoolchildren for hundreds of thousands of dollars, but schoolchildren may well get free versions of professional tools Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, as well as Icarus Verilog, GTKWave and the online edaplayground. com .I reread the previous paragraph and thought: but Cadence SimVision for the summer school in Zelenograd could have been used. It is made better and more convenient, both of its direct competitor Synopsys Design Vision Environment (DVE) * , and funds from Mentor Graphics (free ModelSim and paid Questa), and all cheap and free tools (IcarusVerilog, etc.) If the Moscow branch of Cadence The Design System will give us the right and support to use their software at summer schools in Zelenograd, personally I will be for integrating this into the school curriculum.* For DVE, for example, the text in the source window is buggy / jumping when I run it under Ubuntu. I have to do window resize until it ceases to fail. SimVision does not have this.Here is the start of the SimVision tutorial (22 videos in total):But back to the games. If not Stephen Hugg, then what? I wrote an example of a simple game that I used at a summer school in Zelenograd . The sources of the game are on the github . It looks like this:For two weeks, students figured out the basic principles of design at the level of register transfers and began to make their own, and non-trivial games:Let's talk about the technical details of an example game. A platform-independent game module can be placed (instantiated) in the wrapper of any FPGA board that has a VGA port and two buttons. If the board is completely bare, then you can connect an adapter for VGA and buttons to it through the GPIO (general purpose input / output) wires. The game module consists of:

Of course, I don’t propose to blame Cadence SimVision and Synopsys Design Compiler for schoolchildren for hundreds of thousands of dollars, but schoolchildren may well get free versions of professional tools Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim, as well as Icarus Verilog, GTKWave and the online edaplayground. com .I reread the previous paragraph and thought: but Cadence SimVision for the summer school in Zelenograd could have been used. It is made better and more convenient, both of its direct competitor Synopsys Design Vision Environment (DVE) * , and funds from Mentor Graphics (free ModelSim and paid Questa), and all cheap and free tools (IcarusVerilog, etc.) If the Moscow branch of Cadence The Design System will give us the right and support to use their software at summer schools in Zelenograd, personally I will be for integrating this into the school curriculum.* For DVE, for example, the text in the source window is buggy / jumping when I run it under Ubuntu. I have to do window resize until it ceases to fail. SimVision does not have this.Here is the start of the SimVision tutorial (22 videos in total):But back to the games. If not Stephen Hugg, then what? I wrote an example of a simple game that I used at a summer school in Zelenograd . The sources of the game are on the github . It looks like this:For two weeks, students figured out the basic principles of design at the level of register transfers and began to make their own, and non-trivial games:Let's talk about the technical details of an example game. A platform-independent game module can be placed (instantiated) in the wrapper of any FPGA board that has a VGA port and two buttons. If the board is completely bare, then you can connect an adapter for VGA and buttons to it through the GPIO (general purpose input / output) wires. The game module consists of:- VGA scan generator.

- Two parallel working modules for sprite torpedoes and sprite targets.

- The state machine for the game scenario, with the states "start", "guidance", "flies", "victory / defeat".

- A module that determines if sprites collided.

- A timer to set the duration of the visual effect after winning (blinking raspberry screen) or defeat (yellow screen).

For the next school, all these pictures need to be redrawn using draw.io or Lucidchart into normal microarchitecture diagrams: You

For the next school, all these pictures need to be redrawn using draw.io or Lucidchart into normal microarchitecture diagrams: You also need to add timelines drawn with WaveDrom to the school materials to show how the VGA scan generator works and how the mini-pipeline calculates the coordinates data path inside sprites:

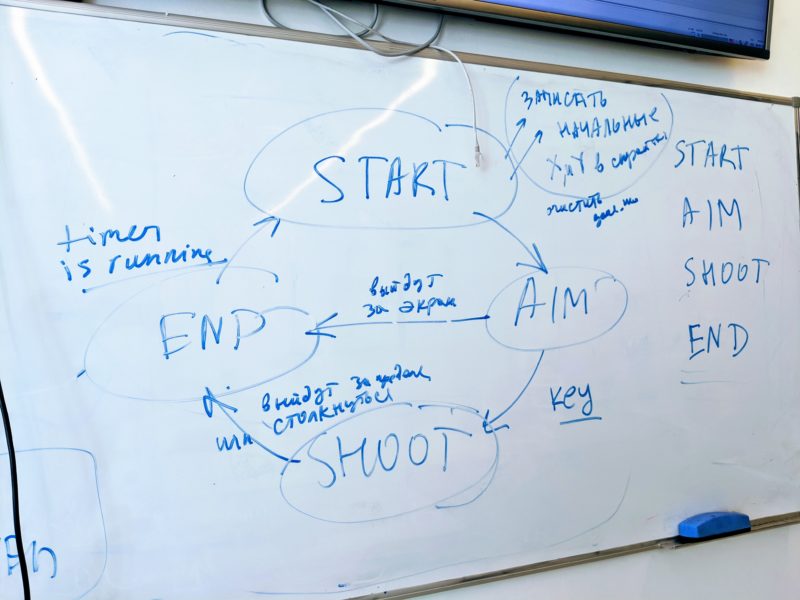

also need to add timelines drawn with WaveDrom to the school materials to show how the VGA scan generator works and how the mini-pipeline calculates the coordinates data path inside sprites: And of course you need to draw diagrams of the finite state machine. I made a dozen variants of the finite state machine of this game, here on the board there is a variant with four states:

And of course you need to draw diagrams of the finite state machine. I made a dozen variants of the finite state machine of this game, here on the board there is a variant with four states: Why did I make many choices? Even with such a simple machine, you can compare different styles of their coding on a veril, as well as illustrate the optimization of states and timing. All this is asked in an interview for a position as a chip designer at Apple, NVidia, Intel, AMD and other companies. Therefore, this area must be known so that the teeth bounce. There are some good Clifford Cummings articles on this subject:

Why did I make many choices? Even with such a simple machine, you can compare different styles of their coding on a veril, as well as illustrate the optimization of states and timing. All this is asked in an interview for a position as a chip designer at Apple, NVidia, Intel, AMD and other companies. Therefore, this area must be known so that the teeth bounce. There are some good Clifford Cummings articles on this subject:- 2019 Newest Article: FiniteStateMachine (FSM) Design & Synthesis using SystemVerilog - Part I by Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

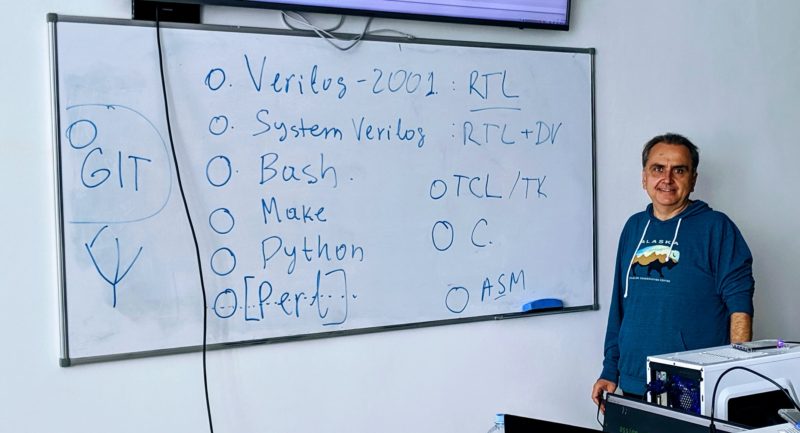

I synthesized different versions of the game’s state machine using the most popular Synopsys Design Compiler tool in the industry and made such a tablet. As we can see, the modern version of DC optimizes all styles very efficiently, so pulling picoseconds on state machines is possible, but not necessary. Although it is possible for more complex finite state machines, tricks from Cummings' articles will be more critical: During school in Zelenograd, we also discussed that in the design of chips, in addition to the description languages of the Verilog and VHDL equipment, many auxiliary languages are used:

During school in Zelenograd, we also discussed that in the design of chips, in addition to the description languages of the Verilog and VHDL equipment, many auxiliary languages are used:Python is used to automate assembly, regression management, and extract information from synthesis and code generation reports, as well as bash, make, and other Unix / Linux kitchens.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ and libraries like SystemC are used to write transaction-level hardware block models. Verification engineers check the blocks designed on the veril against these models.

If you work for a processor company, it’s good for you to know assembler. Even if you are not a low-level programmer and not a verifier, but a processor designer at the level of register transfers (Register Transfer Level - RTL).

Here are links for those interested in using pearl as a preprocessor for verilogue:- G. Spivey. EP3: An extensible Perl preprocessor

- vpp.pl man page

- A Verilog Preprocessor

An example of how to use the built-in verlog pearl to connect 64 ports://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

It would be nice if someone wrote universal scripts for modeling and synthesizing an example (not necessarily my game) on all the main platforms for synthesis, simulation, debugging, analysis of dynamic power consumption, physical design, binding for all boards, etc. This could be used in schools and seminars:

It would be nice if someone wrote universal scripts for modeling and synthesizing an example (not necessarily my game) on all the main platforms for synthesis, simulation, debugging, analysis of dynamic power consumption, physical design, binding for all boards, etc. This could be used in schools and seminars: Here you may have a question: why do I use Linux seminars? Although Windows also has a modeling and synthesis environment for FPGAs, Windows has not taken root in the industry of mass chip design. In the early 1990s, the workstation market for ASIC developers was split between SunOS and HP / UX. Then the electronic companies played for three years with Windows NT, but it did not work. After that, Synopsys and other design software companies spat and switched to Linux - first on Red Hat, then on SuSE and Ubuntu. I suspect, mainly because of a bunch of scripts on the pearl, C-shell, etc., as well as because of the remote work of developers through telnet and X Window.Therefore, for my seminars I go with a bunch of bootable SSDs with Lubuntu, on which all the necessary software is installed. I use legacy boot, but recently it turned out that more and more computers require UEFI boot. Apparently, you will need to make a bootable SSD with UEFI boot.Fast-moving companies use CentOS instead of Red Hat. Perhaps many design tools go under Debian, but I have not tested it.

Here you may have a question: why do I use Linux seminars? Although Windows also has a modeling and synthesis environment for FPGAs, Windows has not taken root in the industry of mass chip design. In the early 1990s, the workstation market for ASIC developers was split between SunOS and HP / UX. Then the electronic companies played for three years with Windows NT, but it did not work. After that, Synopsys and other design software companies spat and switched to Linux - first on Red Hat, then on SuSE and Ubuntu. I suspect, mainly because of a bunch of scripts on the pearl, C-shell, etc., as well as because of the remote work of developers through telnet and X Window.Therefore, for my seminars I go with a bunch of bootable SSDs with Lubuntu, on which all the necessary software is installed. I use legacy boot, but recently it turned out that more and more computers require UEFI boot. Apparently, you will need to make a bootable SSD with UEFI boot.Fast-moving companies use CentOS instead of Red Hat. Perhaps many design tools go under Debian, but I have not tested it. For the seminars, I use Chinese FPGA boards, one of which is held in my hands by a Novosibirsk girl Natasha, who organizes What-Where-When parties in our Silicon Valley .

For the seminars, I use Chinese FPGA boards, one of which is held in my hands by a Novosibirsk girl Natasha, who organizes What-Where-When parties in our Silicon Valley . In the month of March, I walked through the California wildlife along with Russian businessman Sergei Zorin, who took a dozen ZEOWAA boards to Moscow, similar in characteristics to the one that Natasha is holding in their hands.Since there will probably be no seminars in Zelenograd due to the coronavirus this summer, I think I will give this dozen fees to Moscow schoolchildren for free (UPD: schoolchildren from other cities can also, although there is additional fuss with forwarding). With two conditions:

In the month of March, I walked through the California wildlife along with Russian businessman Sergei Zorin, who took a dozen ZEOWAA boards to Moscow, similar in characteristics to the one that Natasha is holding in their hands.Since there will probably be no seminars in Zelenograd due to the coronavirus this summer, I think I will give this dozen fees to Moscow schoolchildren for free (UPD: schoolchildren from other cities can also, although there is additional fuss with forwarding). With two conditions:Before you get a board, you need to go through all three parts of the online course “How do the creators of smart nanochips work” ( “From the transistor to the microcircuit” , “The logical side of digital circuitry” , “The physical side of digital circuitry” ), and get a certificate. We created this course together with RUSNANO, or rather, its educational daughter eNano, the STEMford project.

, , , . , , , ( ) . , , .

, , .

If you want to buy a new book “Logical Synthesis” as an aid to such a project , then for Habr’s readers she has a promotional code - Sintez_2020. In the future, it would be nice to get off using Chinese boards and make a cheap Russian board for such exercises with FPGA, with an open design. I welcome if you share your thoughts in the comments on the board design software and ideas on how to better design and market such a board. For mass use with schoolchildren, it is desirable that it cost no more than $ 30 or 2000 rubles.

In the future, it would be nice to get off using Chinese boards and make a cheap Russian board for such exercises with FPGA, with an open design. I welcome if you share your thoughts in the comments on the board design software and ideas on how to better design and market such a board. For mass use with schoolchildren, it is desirable that it cost no more than $ 30 or 2000 rubles. If you are a student and are interested in the design of microcircuits, you can go to MIET, HSE MIEM, Moscow Engineering Physics Institute, Moscow State University, Moscow Institute of Physics and Technology ( Nikita Polyakov is engaged in such exercises, MPEI, MISiS, ITMO, LETI, Samara University, some Ukrainian universities (KNU, Chernihiv NTU, Kharkov KNURE) and other universities. So I found how my approach to the MIET selection committee in Zelenograd was being repaired:

If you are a student and are interested in the design of microcircuits, you can go to MIET, HSE MIEM, Moscow Engineering Physics Institute, Moscow State University, Moscow Institute of Physics and Technology ( Nikita Polyakov is engaged in such exercises, MPEI, MISiS, ITMO, LETI, Samara University, some Ukrainian universities (KNU, Chernihiv NTU, Kharkov KNURE) and other universities. So I found how my approach to the MIET selection committee in Zelenograd was being repaired: But here is how MIET looks inside: You can

But here is how MIET looks inside: You can find a job there right opposite MIET to the ELVIS NGO, which deals with smart cameras and satellite chips:

find a job there right opposite MIET to the ELVIS NGO, which deals with smart cameras and satellite chips: Or you can come to Silicon Valley. Want to get an interview with Dolina? Practice on FPGA boards!

Or you can come to Silicon Valley. Want to get an interview with Dolina? Practice on FPGA boards!