Das neue Labor für digitale Synthese setzt die Tradition des Tutorials von David Harris und Sarah Harris, Digital Circuitry and Computer Architecture, fort, das die britische Website heruntergeladen hat . Im Labor können Sie die gesamte Theorie von Harris & Harris auf der FPGA-Karte berühren, vom Blinken bis zum Prozessor. Das Konzept der Fördererverarbeitung wird auch im Labor analysiert, ohne das Sie kein Interview bestehen, um als Designer in einem mikroelektronischen Unternehmen zu arbeiten. Am Ende der Weg vom FPGA zum ASIC, Massenstromkreise, die in iPhones, Tesla und AI-Beschleunigern enthalten sind.Das Buch enthält ein Interview mit einem Team aus St. Petersburg, das Intel zu seinem Sieg im Innovate FPGA-Wettbewerb in sein Hauptquartier im Silicon Valley gebracht hat. Buch "Digitale Synthese: Ein praktischer Kurs"Cadence Design Systems, ein führendes Unternehmen in der Automatisierung des Mikroschaltungsdesigns, wird unterstützt (auf dem Foto oben steht die Sibirierin Natasha mit einem FPGA-Board vor dem Hauptsitz von Cadence im Silicon Valley - ihr Video wird in der Post sein).Labnik wurde unter der Schirmherrschaft der Higher School of Economics / MIEM (Alexander Romanov, Veronika Prokhorova und Igor Agamirzyan) gegründet, während verschiedene Kapitel von Lehrern der Universitäten Moskau, Kiew und Samara, der ITMO St. Petersburg, des Polytechnikums Tschernihiw und der Universität von Kalifornien Santa Cruz ( Charles Danchek) verfasst wurden Abendbüro im Silicon Valley). An der Erstellung des Lehrbuchs nahmen Ingenieure des russischen Unternehmens IVA Technologies (Stanislav Zhelnio, Hardwarebeschleuniger AI + Bildungsprojekt schoolMIPS) teil) und FSUE NPTSAP(Abteilung Roscosmos), amerikanische Unternehmen MIPS, Juniper Networks und AMD. Veröffentlichung eines Lehrbuchs DMK-Press.Ich erstellte einen Plan für das Labor und zog Autoren aus früheren Bildungsprojekten an. Danach übertrug ich die Kontrolle auf Alexander Romanov, der mühsame Arbeit leistete und das Projekt fast zwei Jahre lang leitete. Die Erstellung des Lehrbuchs passte natürlich zu den Aktivitäten von Alexander , der 3 Jahre lang das Labor am HSE MIEM leitete , das sich mit eingebetteten Computern, Robotik und FPGAs befasst. Das Labor organisierte mehrere Teams beim Innovate FPGA, von denen eines im regionalen Finale Bronzemedaillengewinner wurde .Das Lehrbuch ist nicht nur für Studenten geeignet, sondern kann auch für Sommercamps mit digitalem Design für fortgeschrittene Studenten verwendet werden. Es ist nicht trivial, Tutorials im Internet von Grund auf zu verstehen, wie man mit der Intel Quartus II-Umgebung arbeitet. Und im Lehrbuch wird alles in Schritten beschrieben. Darüber hinaus hat es alle theoretischen Grundlagen, um etwas Interessantes für Schulkinder zu tun, zusätzlich zu blinkenden Lichtern, die sie schnell stören. Interessant ist zum Beispiel ein Videospiel:

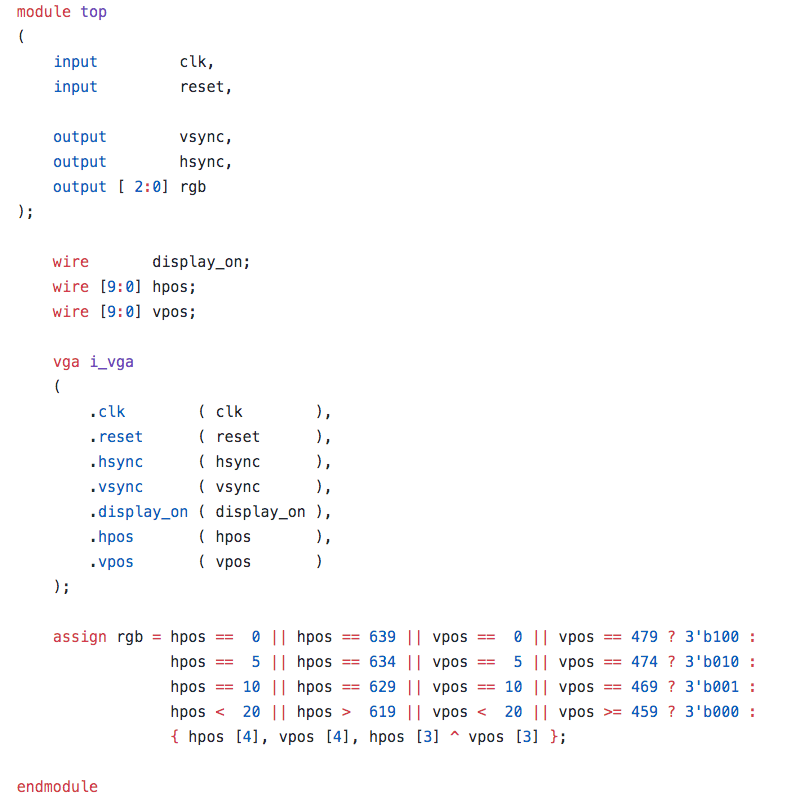

Das neue Labor für digitale Synthese setzt die Tradition des Tutorials von David Harris und Sarah Harris, Digital Circuitry and Computer Architecture, fort, das die britische Website heruntergeladen hat . Im Labor können Sie die gesamte Theorie von Harris & Harris auf der FPGA-Karte berühren, vom Blinken bis zum Prozessor. Das Konzept der Fördererverarbeitung wird auch im Labor analysiert, ohne das Sie kein Interview bestehen, um als Designer in einem mikroelektronischen Unternehmen zu arbeiten. Am Ende der Weg vom FPGA zum ASIC, Massenstromkreise, die in iPhones, Tesla und AI-Beschleunigern enthalten sind.Das Buch enthält ein Interview mit einem Team aus St. Petersburg, das Intel zu seinem Sieg im Innovate FPGA-Wettbewerb in sein Hauptquartier im Silicon Valley gebracht hat. Buch "Digitale Synthese: Ein praktischer Kurs"Cadence Design Systems, ein führendes Unternehmen in der Automatisierung des Mikroschaltungsdesigns, wird unterstützt (auf dem Foto oben steht die Sibirierin Natasha mit einem FPGA-Board vor dem Hauptsitz von Cadence im Silicon Valley - ihr Video wird in der Post sein).Labnik wurde unter der Schirmherrschaft der Higher School of Economics / MIEM (Alexander Romanov, Veronika Prokhorova und Igor Agamirzyan) gegründet, während verschiedene Kapitel von Lehrern der Universitäten Moskau, Kiew und Samara, der ITMO St. Petersburg, des Polytechnikums Tschernihiw und der Universität von Kalifornien Santa Cruz ( Charles Danchek) verfasst wurden Abendbüro im Silicon Valley). An der Erstellung des Lehrbuchs nahmen Ingenieure des russischen Unternehmens IVA Technologies (Stanislav Zhelnio, Hardwarebeschleuniger AI + Bildungsprojekt schoolMIPS) teil) und FSUE NPTSAP(Abteilung Roscosmos), amerikanische Unternehmen MIPS, Juniper Networks und AMD. Veröffentlichung eines Lehrbuchs DMK-Press.Ich erstellte einen Plan für das Labor und zog Autoren aus früheren Bildungsprojekten an. Danach übertrug ich die Kontrolle auf Alexander Romanov, der mühsame Arbeit leistete und das Projekt fast zwei Jahre lang leitete. Die Erstellung des Lehrbuchs passte natürlich zu den Aktivitäten von Alexander , der 3 Jahre lang das Labor am HSE MIEM leitete , das sich mit eingebetteten Computern, Robotik und FPGAs befasst. Das Labor organisierte mehrere Teams beim Innovate FPGA, von denen eines im regionalen Finale Bronzemedaillengewinner wurde .Das Lehrbuch ist nicht nur für Studenten geeignet, sondern kann auch für Sommercamps mit digitalem Design für fortgeschrittene Studenten verwendet werden. Es ist nicht trivial, Tutorials im Internet von Grund auf zu verstehen, wie man mit der Intel Quartus II-Umgebung arbeitet. Und im Lehrbuch wird alles in Schritten beschrieben. Darüber hinaus hat es alle theoretischen Grundlagen, um etwas Interessantes für Schulkinder zu tun, zusätzlich zu blinkenden Lichtern, die sie schnell stören. Interessant ist zum Beispiel ein Videospiel: Die Idee, Verilo mit VGA-Spielen zu lernen, ist nicht neu - viele Universitäten haben ein solches Labor, beispielsweise im 6.111 Introductory Digital Systems Laboratory am Massachusetts Institute of Technology (MIT). Außerdem wurde vor zwei Jahren das Buch Designing Video Game Hardware in Verilog Paperback von Steven Hugg veröffentlicht, mit ziemlich entwickelten Spielen mit Panzern, Rennwagen, einem pseudozufälligen Sternenhimmelgenerator unter Verwendung von LFSR, einem Bildspeicher und sogar einer Hardware-Software-Schnittstelle. Darüber hinaus sind VGA-Spiele in Demos von Herstellern der FPGAs Xilinx und Intel / Altera enthalten, genauer gesagt von ihren Partnerunternehmen Digilent und Terasic.

Die Idee, Verilo mit VGA-Spielen zu lernen, ist nicht neu - viele Universitäten haben ein solches Labor, beispielsweise im 6.111 Introductory Digital Systems Laboratory am Massachusetts Institute of Technology (MIT). Außerdem wurde vor zwei Jahren das Buch Designing Video Game Hardware in Verilog Paperback von Steven Hugg veröffentlicht, mit ziemlich entwickelten Spielen mit Panzern, Rennwagen, einem pseudozufälligen Sternenhimmelgenerator unter Verwendung von LFSR, einem Bildspeicher und sogar einer Hardware-Software-Schnittstelle. Darüber hinaus sind VGA-Spiele in Demos von Herstellern der FPGAs Xilinx und Intel / Altera enthalten, genauer gesagt von ihren Partnerunternehmen Digilent und Terasic. Insbesondere im Labor vom MITEs wird sehr deutlich gezeigt, dass Sie zum Zeichnen auf dem Display lediglich eine Funktion in Form eines Diagramms implementieren müssen, die die Koordinaten X und Y eines Punkts auf dem Bildschirm als Argument verwendet und die Farbe dieses Punkts (RGB) zurückgibt. Im einfachsten Fall ist diese Funktion eine Kombinationsfunktion. Eine solche Funktion zeichnet beispielsweise Malevichs Meisterwerk: „Farbe ist schwarz (RGB = 0,0,0), wenn x> = 200 und x <= 400 und y> = 200 und y <400, andernfalls weiß (RGB = 1,1,1). Wir werden eine solche Schaltung ferner als "Mischer" bezeichnen, da sie Eingänge von Generatoren mit unterschiedlichen Bildern "mischt".Um die Mischerargumente X und Y selbst zu erzeugen, wird eine einfache Zwei-Zähler-Schaltung verwendet, die das CLK-Taktsignal verwendet. Zusätzlich zu den X- und Y-Koordinaten erzeugt diese Schaltung auch HSYNC- und VSYNC-Signale für die VGA-Anzeige. Die HSYNC- und VSYNC-Signale sind seit der Zeit der Kathodenstrahlröhre erhalten geblieben. Sie teilen dem virtuellen Strahl mit, wann er horizontal zum nächsten Punkt / Pixel auf dem Bildschirm und dann vertikal zur nächsten Zeile wechseln soll.In einem schwierigen Fall verwendet der Mischer nicht nur die Werte seiner Eingänge X und Y, sondern auch die Werte der Zustandselemente (D-Flip-Flops und Speicher), die unter Verwendung des CLK-Taktsignals aufgezeichnet werden. In diesem Fall tritt die Uhr auch in den Mischer ein. Schaltungen mit Taktsignalen und Zustandselementen werden als sequentiell bezeichnet (diese Schaltungen durchlaufen eine Folge von Zuständen, die durch ein pulsierendes Taktsignal klar voneinander getrennt sind). Auf Serienmischern können Sie bewegte Bilder beliebiger Komplexität implementieren.Hier sind die Bilder aus dem MIT-Shnaya-Labor (das gleiche befindet sich auf dem Haufen anderer Universitäten), die die Funktion des HSYNC / VSYNC-Generators, des Mischers (derselben Einheit, die RGB als Funktion von X / HCOUNT und Y / VCOUNT berechnet) sowie die Ausgabe von HSYNC veranschaulichen. VSYNC und RGB auf dem Bildschirm. Das Bild verwendet einen Schalter / Multiplexer zwischen drei Mischern - einer zeichnet Streifen, ein anderer zeichnet ein Rechteck und der dritte zeichnet ein Bild auf dem Bildschirm, während Tischtennis gespielt wird:

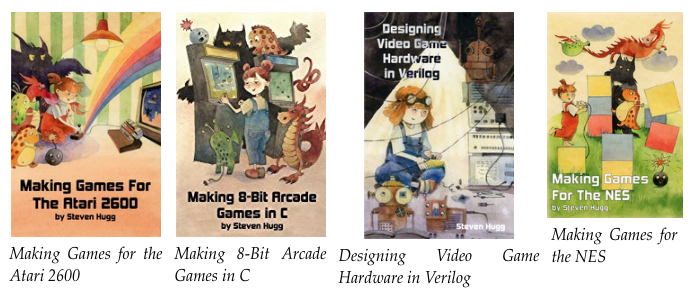

Insbesondere im Labor vom MITEs wird sehr deutlich gezeigt, dass Sie zum Zeichnen auf dem Display lediglich eine Funktion in Form eines Diagramms implementieren müssen, die die Koordinaten X und Y eines Punkts auf dem Bildschirm als Argument verwendet und die Farbe dieses Punkts (RGB) zurückgibt. Im einfachsten Fall ist diese Funktion eine Kombinationsfunktion. Eine solche Funktion zeichnet beispielsweise Malevichs Meisterwerk: „Farbe ist schwarz (RGB = 0,0,0), wenn x> = 200 und x <= 400 und y> = 200 und y <400, andernfalls weiß (RGB = 1,1,1). Wir werden eine solche Schaltung ferner als "Mischer" bezeichnen, da sie Eingänge von Generatoren mit unterschiedlichen Bildern "mischt".Um die Mischerargumente X und Y selbst zu erzeugen, wird eine einfache Zwei-Zähler-Schaltung verwendet, die das CLK-Taktsignal verwendet. Zusätzlich zu den X- und Y-Koordinaten erzeugt diese Schaltung auch HSYNC- und VSYNC-Signale für die VGA-Anzeige. Die HSYNC- und VSYNC-Signale sind seit der Zeit der Kathodenstrahlröhre erhalten geblieben. Sie teilen dem virtuellen Strahl mit, wann er horizontal zum nächsten Punkt / Pixel auf dem Bildschirm und dann vertikal zur nächsten Zeile wechseln soll.In einem schwierigen Fall verwendet der Mischer nicht nur die Werte seiner Eingänge X und Y, sondern auch die Werte der Zustandselemente (D-Flip-Flops und Speicher), die unter Verwendung des CLK-Taktsignals aufgezeichnet werden. In diesem Fall tritt die Uhr auch in den Mischer ein. Schaltungen mit Taktsignalen und Zustandselementen werden als sequentiell bezeichnet (diese Schaltungen durchlaufen eine Folge von Zuständen, die durch ein pulsierendes Taktsignal klar voneinander getrennt sind). Auf Serienmischern können Sie bewegte Bilder beliebiger Komplexität implementieren.Hier sind die Bilder aus dem MIT-Shnaya-Labor (das gleiche befindet sich auf dem Haufen anderer Universitäten), die die Funktion des HSYNC / VSYNC-Generators, des Mischers (derselben Einheit, die RGB als Funktion von X / HCOUNT und Y / VCOUNT berechnet) sowie die Ausgabe von HSYNC veranschaulichen. VSYNC und RGB auf dem Bildschirm. Das Bild verwendet einen Schalter / Multiplexer zwischen drei Mischern - einer zeichnet Streifen, ein anderer zeichnet ein Rechteck und der dritte zeichnet ein Bild auf dem Bildschirm, während Tischtennis gespielt wird: Im Code sieht der einfachste Mixer so aus. Er zeichnet mehrfarbige Quadrate aus Mischungen von Rot, Blau und Grün sowie Linien aus reinen Farben:

Im Code sieht der einfachste Mixer so aus. Er zeichnet mehrfarbige Quadrate aus Mischungen von Rot, Blau und Grün sowie Linien aus reinen Farben: Auf diese Weise können Sie eine Vielzahl von farbenfrohen statischen Bildern zeichnen. Hier sind die Bilder, die Schüler an einer Sommerschule in Zelenograd unmittelbar nach einem kurzen Vortrag gemalt haben, in dem erklärt wird, wie es geht:

Auf diese Weise können Sie eine Vielzahl von farbenfrohen statischen Bildern zeichnen. Hier sind die Bilder, die Schüler an einer Sommerschule in Zelenograd unmittelbar nach einem kurzen Vortrag gemalt haben, in dem erklärt wird, wie es geht: Nun, Schulkinder können die RGB-Funktion (X, Y) codieren und statische Bilder zeichnen. Aber was ist als nächstes zu tun, was ist der nächste Schritt? Wir untersuchten die Möglichkeit, Materialien von MIT, Digilent + Xilinx, Altera + Terasic und Steven Hugg zu verwenden, und kamen zu dem Schluss, dass sie nicht in ihrer reinen Form verwendet werden können. Universitätslabors sind im Universitätsprogramm enthalten, und Materialien von FPGA-Anbietern sind nicht gut geschrieben und enthalten auch keine Tipps, wie Sie den Code im Format einer Sommerschule ändern können, damit die Schüler ihre Spiele erfinden. Das Buch von Stephen Hugg hat zwei Nachteile, die die Kehrseite seiner Tugenden sind (Lebendigkeit und Buntheit):Im Allgemeinen entspricht der Verilog von Stephen Hugg der Programmierung der Prozessoren der alten 8-Bit-Konsolen von Atari und Nintendo. Daher konzentriert sich Hugg nicht auf die Ausbildung zukünftiger Superdesigner, sondern auf Nostalgiker, Retro-Informatiker und andere Reenactors. Der Unterschied zwischen seiner Umgebung und professionellen Designtools ist noch größer als zwischen der Arduino-Programmierumgebung und den Toolkits für STM32.

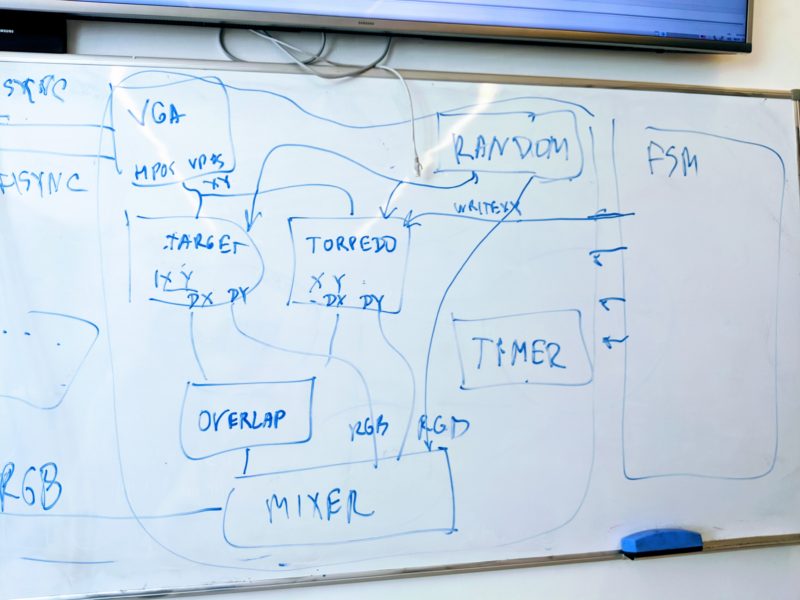

Nun, Schulkinder können die RGB-Funktion (X, Y) codieren und statische Bilder zeichnen. Aber was ist als nächstes zu tun, was ist der nächste Schritt? Wir untersuchten die Möglichkeit, Materialien von MIT, Digilent + Xilinx, Altera + Terasic und Steven Hugg zu verwenden, und kamen zu dem Schluss, dass sie nicht in ihrer reinen Form verwendet werden können. Universitätslabors sind im Universitätsprogramm enthalten, und Materialien von FPGA-Anbietern sind nicht gut geschrieben und enthalten auch keine Tipps, wie Sie den Code im Format einer Sommerschule ändern können, damit die Schüler ihre Spiele erfinden. Das Buch von Stephen Hugg hat zwei Nachteile, die die Kehrseite seiner Tugenden sind (Lebendigkeit und Buntheit):Im Allgemeinen entspricht der Verilog von Stephen Hugg der Programmierung der Prozessoren der alten 8-Bit-Konsolen von Atari und Nintendo. Daher konzentriert sich Hugg nicht auf die Ausbildung zukünftiger Superdesigner, sondern auf Nostalgiker, Retro-Informatiker und andere Reenactors. Der Unterschied zwischen seiner Umgebung und professionellen Designtools ist noch größer als zwischen der Arduino-Programmierumgebung und den Toolkits für STM32. Natürlich möchte ich Cadence SimVision und Synopsys Design Compiler nicht für Hunderttausende von Dollar für Schulkinder verantwortlich machen, aber Schulkinder erhalten möglicherweise kostenlose Versionen der professionellen Tools Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim sowie Icarus Verilog, GTKWave und den Online- Edaplayground. com .Ich habe den vorherigen Absatz noch einmal gelesen und dachte: Aber Cadence SimVision für die Sommerschule in Zelenograd hätte verwendet werden können. Es wird besser und bequemer gemacht, sowohl von seinem direkten Konkurrenten Synopsys Design Vision Environment (DVE) * als auch von Geldern von Mentor Graphics (kostenloses ModelSim und kostenpflichtiges Questa) und allen billigen und kostenlosen Tools (IcarusVerilog usw.), wenn die Moskauer Niederlassung von Cadence Das Design-System gibt uns das Recht und die Unterstützung, ihre Software an Sommerschulen in Zelenograd einzusetzen. Ich persönlich werde dafür verantwortlich sein, dies in den Lehrplan der Schule zu integrieren.* Bei DVE ist der Text im Quellfenster beispielsweise fehlerhaft / springend, wenn ich ihn unter Ubuntu ausführe. Ich muss die Fenstergröße ändern, bis sie nicht mehr fehlschlägt. SimVision hat dies nicht.Hier ist der Beginn des SimVision-Tutorials (insgesamt 22 Videos):Aber zurück zu den Spielen. Wenn nicht Stephen Hugg, was dann? Ich habe ein Beispiel für ein einfaches Spiel geschrieben, das ich an einer Sommerschule in Zelenograd verwendet habe . Die Quellen des Spiels sind auf dem Github . Es sieht aus wie das:Zwei Wochen lang haben die Schüler die Grundprinzipien des Designs auf der Ebene der Registerübertragungen herausgefunden und begonnen, ihre eigenen und nicht trivialen Spiele zu entwickeln:Lassen Sie uns über die technischen Details eines Beispielspiels sprechen. Ein plattformunabhängiges Spielmodul kann im Wrapper eines FPGA-Boards mit einem VGA-Anschluss und zwei Tasten platziert (instanziiert) werden. Wenn die Karte vollständig leer ist, können Sie einen Adapter für VGA und Tasten über die GPIO-Kabel (Universal Purpose Input / Output) daran anschließen. Das Spielmodul besteht aus:

Natürlich möchte ich Cadence SimVision und Synopsys Design Compiler nicht für Hunderttausende von Dollar für Schulkinder verantwortlich machen, aber Schulkinder erhalten möglicherweise kostenlose Versionen der professionellen Tools Xilinx Vivado, Intel / Altera Quartus II, Mentor ModelSim sowie Icarus Verilog, GTKWave und den Online- Edaplayground. com .Ich habe den vorherigen Absatz noch einmal gelesen und dachte: Aber Cadence SimVision für die Sommerschule in Zelenograd hätte verwendet werden können. Es wird besser und bequemer gemacht, sowohl von seinem direkten Konkurrenten Synopsys Design Vision Environment (DVE) * als auch von Geldern von Mentor Graphics (kostenloses ModelSim und kostenpflichtiges Questa) und allen billigen und kostenlosen Tools (IcarusVerilog usw.), wenn die Moskauer Niederlassung von Cadence Das Design-System gibt uns das Recht und die Unterstützung, ihre Software an Sommerschulen in Zelenograd einzusetzen. Ich persönlich werde dafür verantwortlich sein, dies in den Lehrplan der Schule zu integrieren.* Bei DVE ist der Text im Quellfenster beispielsweise fehlerhaft / springend, wenn ich ihn unter Ubuntu ausführe. Ich muss die Fenstergröße ändern, bis sie nicht mehr fehlschlägt. SimVision hat dies nicht.Hier ist der Beginn des SimVision-Tutorials (insgesamt 22 Videos):Aber zurück zu den Spielen. Wenn nicht Stephen Hugg, was dann? Ich habe ein Beispiel für ein einfaches Spiel geschrieben, das ich an einer Sommerschule in Zelenograd verwendet habe . Die Quellen des Spiels sind auf dem Github . Es sieht aus wie das:Zwei Wochen lang haben die Schüler die Grundprinzipien des Designs auf der Ebene der Registerübertragungen herausgefunden und begonnen, ihre eigenen und nicht trivialen Spiele zu entwickeln:Lassen Sie uns über die technischen Details eines Beispielspiels sprechen. Ein plattformunabhängiges Spielmodul kann im Wrapper eines FPGA-Boards mit einem VGA-Anschluss und zwei Tasten platziert (instanziiert) werden. Wenn die Karte vollständig leer ist, können Sie einen Adapter für VGA und Tasten über die GPIO-Kabel (Universal Purpose Input / Output) daran anschließen. Das Spielmodul besteht aus:- VGA-Scan-Generator.

- Zwei parallele Arbeitsmodule für Sprite-Torpedos und Sprite-Ziele.

- Die Zustandsmaschine für das Spielszenario mit den Zuständen "Start", "Führung", "Fliegen", "Sieg / Niederlage".

- Ein Modul, das bestimmt, ob Sprites kollidieren.

- Ein Timer zum Einstellen der Dauer des visuellen Effekts nach dem Gewinnen (blinkender Himbeerbildschirm) oder dem Besiegen (gelber Bildschirm).

Für die nächste Schule müssen alle diese Bilder mit draw.io oder Lucidchart in normale Mikroarchitekturdiagramme neu gezeichnet werden: Sie müssen

Für die nächste Schule müssen alle diese Bilder mit draw.io oder Lucidchart in normale Mikroarchitekturdiagramme neu gezeichnet werden: Sie müssen auch die mit WaveDrom gezeichneten Zeitdiagramme für Schulmaterialien hinzufügen, um zu zeigen, wie der VGA-Scangenerator funktioniert und wie die Mini-Pipeline die Koordinaten berechnet Datenpfad in Sprites:

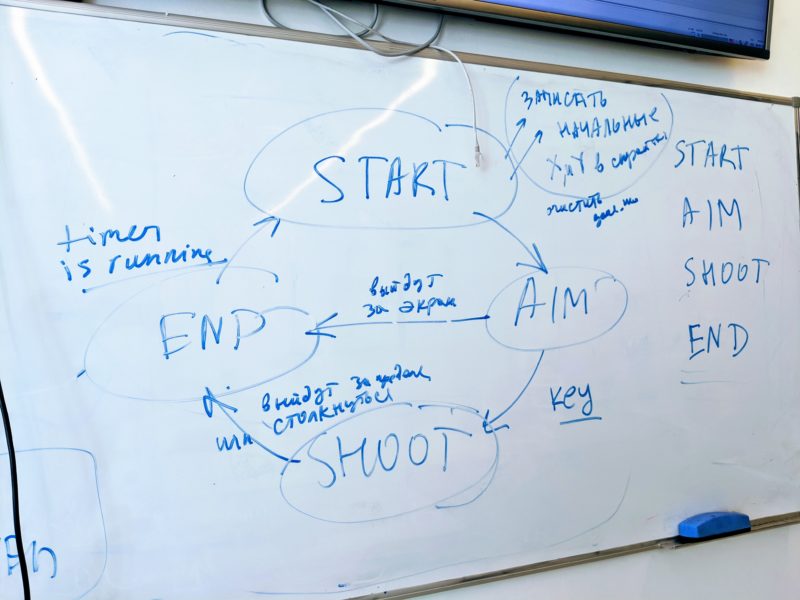

auch die mit WaveDrom gezeichneten Zeitdiagramme für Schulmaterialien hinzufügen, um zu zeigen, wie der VGA-Scangenerator funktioniert und wie die Mini-Pipeline die Koordinaten berechnet Datenpfad in Sprites: Und natürlich müssen Sie Diagramme der Finite-State-Maschine zeichnen. Ich habe ein Dutzend Varianten der Finite-State-Maschine dieses Spiels gemacht, hier auf dem Brett gibt es eine Variante mit vier Zuständen:

Und natürlich müssen Sie Diagramme der Finite-State-Maschine zeichnen. Ich habe ein Dutzend Varianten der Finite-State-Maschine dieses Spiels gemacht, hier auf dem Brett gibt es eine Variante mit vier Zuständen: Warum habe ich viele Entscheidungen getroffen? Selbst mit solch einer einfachen Maschine können Sie verschiedene Arten ihrer Codierung auf einem Veril vergleichen und die Optimierung von Zuständen und Timing veranschaulichen. All dies wird in einem Interview um eine Stelle als Chipdesigner bei Apple, NVidia, Intel, AMD und anderen Unternehmen gebeten. Daher muss dieser Bereich bekannt sein, damit die Zähne abprallen. Es gibt einige gute Artikel von Clifford Cummings zu diesem Thema:

Warum habe ich viele Entscheidungen getroffen? Selbst mit solch einer einfachen Maschine können Sie verschiedene Arten ihrer Codierung auf einem Veril vergleichen und die Optimierung von Zuständen und Timing veranschaulichen. All dies wird in einem Interview um eine Stelle als Chipdesigner bei Apple, NVidia, Intel, AMD und anderen Unternehmen gebeten. Daher muss dieser Bereich bekannt sein, damit die Zähne abprallen. Es gibt einige gute Artikel von Clifford Cummings zu diesem Thema:- 2019 Neuester Artikel: Design und Synthese von FiniteStateMachine (FSM) mit SystemVerilog - Teil I von Clifford E. Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

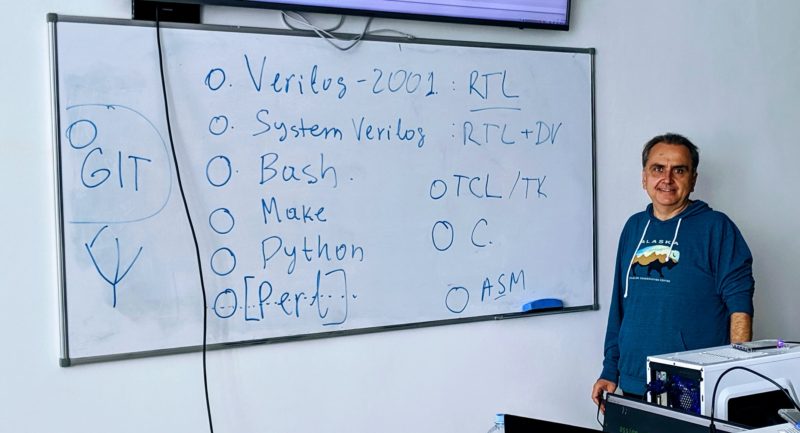

Ich habe verschiedene Versionen der Zustandsmaschine des Spiels mit dem branchenweit beliebtesten Synopsys Design Compiler-Tool synthetisiert und ein solches Tablet hergestellt. Wie wir sehen können, optimiert die moderne Version von DC alle Stile sehr effizient, sodass das Ziehen von Pikosekunden auf Zustandsautomaten möglich, aber nicht erforderlich ist. Obwohl es für komplexere Finite-State-Maschinen möglich ist, werden Tricks aus Cummings 'Artikeln kritischer sein: Während der Schule in Zelenograd haben wir auch diskutiert, dass beim Design von Chips neben Verilog- und VHDL-Hardwarebeschreibungssprachen viele Hilfssprachen verwendet werden:

Während der Schule in Zelenograd haben wir auch diskutiert, dass beim Design von Chips neben Verilog- und VHDL-Hardwarebeschreibungssprachen viele Hilfssprachen verwendet werden:Python wird verwendet, um die Assemblierung, das Regressionsmanagement und das Extrahieren von Informationen aus Synthese- und Codegenerierungsberichten sowie aus Bash-, Make- und anderen Unix / Linux-Küchen zu automatisieren.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

C / C ++ und Bibliotheken wie SystemC werden zum Schreiben von Hardwareblockmodellen auf Transaktionsebene verwendet. Die Prüfer überprüfen die auf dem Veril entworfenen Blöcke anhand dieser Modelle.

Wenn Sie für eine Prozessorfirma arbeiten, ist es gut, dass Sie den Assembler kennen. Auch wenn Sie kein Low-Level-Programmierer und kein Verifizierer sind, sondern ein Prozessor-Designer auf der Ebene der Registerübertragungen (Register Transfer Level - RTL).

Hier sind Links für diejenigen, die Pearl als Präprozessor für Verilogue verwenden möchten:- G. Spivey. EP3: Ein erweiterbarer Perl-Präprozessor

- vpp.pl Manpage

- Ein Verilog-Präprozessor

Ein Beispiel für die Verwendung der integrierten Verlog-Perle zum Verbinden von 64 Ports://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Es wäre schön, wenn jemand universelle Skripte zum Modellieren und Synthetisieren eines Beispiels (nicht unbedingt meines Spiels) auf allen Hauptplattformen für Synthese, Simulation, Debugging, Analyse des dynamischen Stromverbrauchs, physisches Design, Bindung für alle Boards usw. schreiben würde. Dies könnte in Schulen und Seminaren verwendet werden:

Es wäre schön, wenn jemand universelle Skripte zum Modellieren und Synthetisieren eines Beispiels (nicht unbedingt meines Spiels) auf allen Hauptplattformen für Synthese, Simulation, Debugging, Analyse des dynamischen Stromverbrauchs, physisches Design, Bindung für alle Boards usw. schreiben würde. Dies könnte in Schulen und Seminaren verwendet werden: Hier haben Sie vielleicht eine Frage: Warum verwende ich Linux-Seminare? Obwohl Windows auch über eine Modellierungs- und Syntheseumgebung für FPGAs verfügt, hat Windows in der Branche des Massenchip-Designs keine Wurzeln geschlagen. In den frühen neunziger Jahren wurde der Workstation-Markt für ASIC-Entwickler zwischen SunOS und HP / UX aufgeteilt. Dann spielten die Elektronikfirmen drei Jahre lang mit Windows NT, aber es funktionierte nicht. Danach spuckten Synopsys und andere Design-Software-Unternehmen aus und wechselten zu Linux - zuerst auf Red Hat, dann auf SuSE und Ubuntu. Ich vermute, hauptsächlich wegen einer Reihe von Skripten auf der Perle, der C-Shell usw. sowie wegen der Remote-Arbeit der Entwickler über Telnet und X Window.Daher gehe ich für meine Seminare mit einer Reihe von bootfähigen SSDs mit Lubuntu, auf denen die gesamte erforderliche Software installiert ist. Ich verwende Legacy-Boot, aber kürzlich stellte sich heraus, dass immer mehr Computer einen UEFI-Boot benötigen. Anscheinend müssen Sie eine bootfähige SSD mit UEFI-Boot erstellen.Schnelllebige Unternehmen verwenden CentOS anstelle von Red Hat. Vielleicht fallen viele Design-Tools unter Debian, aber ich habe es nicht getestet.

Hier haben Sie vielleicht eine Frage: Warum verwende ich Linux-Seminare? Obwohl Windows auch über eine Modellierungs- und Syntheseumgebung für FPGAs verfügt, hat Windows in der Branche des Massenchip-Designs keine Wurzeln geschlagen. In den frühen neunziger Jahren wurde der Workstation-Markt für ASIC-Entwickler zwischen SunOS und HP / UX aufgeteilt. Dann spielten die Elektronikfirmen drei Jahre lang mit Windows NT, aber es funktionierte nicht. Danach spuckten Synopsys und andere Design-Software-Unternehmen aus und wechselten zu Linux - zuerst auf Red Hat, dann auf SuSE und Ubuntu. Ich vermute, hauptsächlich wegen einer Reihe von Skripten auf der Perle, der C-Shell usw. sowie wegen der Remote-Arbeit der Entwickler über Telnet und X Window.Daher gehe ich für meine Seminare mit einer Reihe von bootfähigen SSDs mit Lubuntu, auf denen die gesamte erforderliche Software installiert ist. Ich verwende Legacy-Boot, aber kürzlich stellte sich heraus, dass immer mehr Computer einen UEFI-Boot benötigen. Anscheinend müssen Sie eine bootfähige SSD mit UEFI-Boot erstellen.Schnelllebige Unternehmen verwenden CentOS anstelle von Red Hat. Vielleicht fallen viele Design-Tools unter Debian, aber ich habe es nicht getestet. Für Seminare verwende ich chinesische FPGA-Boards, von denen eines von einem Nowosibirsker Mädchen, Natasha, in meinen Händen gehalten wird, das What-Where-When-Partys im Silicon Valley veranstaltet .

Für Seminare verwende ich chinesische FPGA-Boards, von denen eines von einem Nowosibirsker Mädchen, Natasha, in meinen Händen gehalten wird, das What-Where-When-Partys im Silicon Valley veranstaltet . Im März ging ich zusammen mit dem russischen Geschäftsmann Sergei Zorin durch die kalifornische Tierwelt, der ein Dutzend ZEOWAA-Bretter nach Moskau gebracht hat, ähnlich wie Natascha in ihren Händen hält.Da es in diesem Sommer aufgrund des Coronavirus wahrscheinlich keine Seminare in Zelenograd geben wird, werde ich Moskau-Schulkindern dieses Dutzend Gebühren kostenlos zur Verfügung stellen (UPD: Schulkinder aus anderen Städten können dies auch, obwohl es zusätzliche Probleme mit der Weiterleitung gibt). Mit zwei Bedingungen:

Im März ging ich zusammen mit dem russischen Geschäftsmann Sergei Zorin durch die kalifornische Tierwelt, der ein Dutzend ZEOWAA-Bretter nach Moskau gebracht hat, ähnlich wie Natascha in ihren Händen hält.Da es in diesem Sommer aufgrund des Coronavirus wahrscheinlich keine Seminare in Zelenograd geben wird, werde ich Moskau-Schulkindern dieses Dutzend Gebühren kostenlos zur Verfügung stellen (UPD: Schulkinder aus anderen Städten können dies auch, obwohl es zusätzliche Probleme mit der Weiterleitung gibt). Mit zwei Bedingungen:Bevor Sie ein Board erhalten, müssen Sie alle drei Teile des Online-Kurses „Wie arbeiten die Entwickler intelligenter Nanochips?“ ( „Vom Transistor zum Mikroschaltkreis“ , „Die logische Seite der digitalen Schaltung“ , „Die physikalische Seite der digitalen Schaltung“ ) durchgehen und ein Zertifikat erhalten. Wir haben diesen Kurs zusammen mit RUSNANO oder besser gesagt seiner pädagogischen Tochter eNano, dem STEMford-Projekt, erstellt.

, , , . , , , ( ) . , , .

, , .

Wenn Sie ein neues Buch "Logical Synthesis" als Hilfe für ein solches Projekt kaufen möchten , hat sie für Habrs Leser einen Aktionscode - Sintez_2020. In Zukunft wäre es schön, mit chinesischen Boards auszusteigen und ein billiges russisches Board für solche Übungen mit FPGA mit offenem Design herzustellen. Ich freue mich, wenn Sie Ihre Gedanken in den Kommentaren zur Board-Design-Software und Ideen zur besseren Gestaltung und Vermarktung eines solchen Boards teilen. Für den Massengebrauch mit Schulkindern ist es wünschenswert, dass es nicht mehr als 30 oder 2000 Rubel kostet.

In Zukunft wäre es schön, mit chinesischen Boards auszusteigen und ein billiges russisches Board für solche Übungen mit FPGA mit offenem Design herzustellen. Ich freue mich, wenn Sie Ihre Gedanken in den Kommentaren zur Board-Design-Software und Ideen zur besseren Gestaltung und Vermarktung eines solchen Boards teilen. Für den Massengebrauch mit Schulkindern ist es wünschenswert, dass es nicht mehr als 30 oder 2000 Rubel kostet. Wenn Sie Student sind und sich für das Design von Mikroschaltungen interessieren, können Sie sich an MIET, HSE MIEM, das Moskauer Institut für Ingenieurphysik, die Moskauer Staatliche Universität und das Moskauer Institut für Physik und Technologie wenden ( Nikita Polyakov nimmt an solchen Übungen teil, MPEI, MISiS, ITMO, LETI, Samara University, einige ukrainische Universitäten (KNU, Chernihiv NTU, Kharkov KNURE) und andere Universitäten. So fand ich heraus, wie meine Herangehensweise an das MIET-Auswahlkomitee in Zelenograd repariert wurde:

Wenn Sie Student sind und sich für das Design von Mikroschaltungen interessieren, können Sie sich an MIET, HSE MIEM, das Moskauer Institut für Ingenieurphysik, die Moskauer Staatliche Universität und das Moskauer Institut für Physik und Technologie wenden ( Nikita Polyakov nimmt an solchen Übungen teil, MPEI, MISiS, ITMO, LETI, Samara University, einige ukrainische Universitäten (KNU, Chernihiv NTU, Kharkov KNURE) und andere Universitäten. So fand ich heraus, wie meine Herangehensweise an das MIET-Auswahlkomitee in Zelenograd repariert wurde: Aber so sieht MIET aus: Dort

Aber so sieht MIET aus: Dort finden Sie direkt gegenüber MIET einen Job bei der ELVIS-NGO, die sich mit intelligenten Kameras und Satelliten-Chips befasst:

finden Sie direkt gegenüber MIET einen Job bei der ELVIS-NGO, die sich mit intelligenten Kameras und Satelliten-Chips befasst: Oder Sie kommen ins Silicon Valley. Willst du ein Interview mit Dolina bekommen? Übe auf FPGA-Boards!

Oder Sie kommen ins Silicon Valley. Willst du ein Interview mit Dolina bekommen? Übe auf FPGA-Boards!