يواصل مختبر التوليف الرقمي الجديد تقاليد البرنامج التعليمي لديفيد هاريس وسارة هاريس ، الدوائر الرقمية وهندسة الكمبيوتر ، التي قامت بتنزيل الموقع البريطاني . يتيح لك المختبر لمس نظرية هاريس وهاريس بالكامل على لوحة FPGA ، من الأضواء الوامضة إلى المعالج. يتم أيضًا تحليل مفهوم معالجة الناقل في المختبر ، والذي بدونه لن تجتاز مقابلة للعمل كمصمم في أي شركة إلكترونية دقيقة. في النهاية ، المسار من FPGA إلى ASIC ، ودارات الكتلة الموجودة في أجهزة تسريع أجهزة iPhones و Tesla و AI.يحتوي الكتاب على مقابلة مع فريق من سانت بطرسبرغ جلبته شركة إنتل إلى مقرها الرئيسي في وادي السليكون لفوزهم في مسابقة Innovate FPGA. كتاب "التوليف الرقمي: دورة عملية"Cadence Design Systems ، شركة رائدة في أتمتة تصميم الدوائر المصغرة ، مدعومة (في الصورة أعلاه ، تقف سيبيريا ناتاشا مع لوحة FPGA أمام المقر الرئيسي لـ Cadence في وادي السيليكون - سيكون الفيديو الخاص بها في البريد).تم إنشاء Labnik تحت رعاية المدرسة العليا للاقتصاد / MIEM (ألكسندر رومانوف ، فيرونيكا بروخوروفا وإيجور أغاميرزيان) ، بينما كتب فصول مختلفة من قبل معلمين من جامعات موسكو وكييف وسمارة ، وسانت بطرسبرغ ITMO ، و Chernihiv Polytechnic ، وجامعة كاليفورنيا سانتا كروز ( تشارلز دانشيك ، مكتب مسائي في وادي السيليكون). حضر إنشاء الكتاب المدرسي مهندسون من شركة IVA Technologies الروسية (ستانيسلاف زيلنيو ، مسرع الأجهزة AI + مدرسة المشروع التعليمي MIPS) و FSUE NPTSAP(قسم Roscosmos) والشركات الأمريكية MIPS و Juniper Networks و AMD. نشر كتاب DMK-Press.لقد وضعت خطة للمختبر وجذبت المؤلفين من المشاريع التعليمية السابقة ، وبعد ذلك نقلت السيطرة إلى ألكسندر رومانوف ، الذي قام بعمل شاق ، وأدار المشروع لمدة عامين تقريبًا. يتناسب إنشاء الكتاب المدرسي بشكل طبيعي مع أنشطة ألكسندر ، الذي رفع المختبر في HSE MIEM لمدة 3 سنوات ، والذي يتعامل مع أجهزة الكمبيوتر المدمجة والروبوتات و FPGA. نظم المختبر عدة فرق في Innovate FPGA ، وأصبح أحدها حاصل على ميدالية برونزية في النهائيات الإقليمية.الكتاب الدراسي ليس مناسبًا للطلاب فقط - يمكن استخدامه في المعسكرات الصيفية للتصميم الرقمي للطلاب المتقدمين. إن فهم البرامج التعليمية على الإنترنت من البداية حول كيفية العمل مع بيئة Intel Quartus II ليس أمرًا تافهًا. وفي الكتاب الدراسي يتم وصف كل شيء في الخطوات. بالإضافة إلى ذلك ، فإنه يحتوي على كل الأسس النظرية للقيام بشيء مثير للاهتمام لأطفال المدارس ، بالإضافة إلى الأضواء الوامضة التي تزعجهم بسرعة. من المثير للاهتمام على سبيل المثال لعبة فيديو:

يواصل مختبر التوليف الرقمي الجديد تقاليد البرنامج التعليمي لديفيد هاريس وسارة هاريس ، الدوائر الرقمية وهندسة الكمبيوتر ، التي قامت بتنزيل الموقع البريطاني . يتيح لك المختبر لمس نظرية هاريس وهاريس بالكامل على لوحة FPGA ، من الأضواء الوامضة إلى المعالج. يتم أيضًا تحليل مفهوم معالجة الناقل في المختبر ، والذي بدونه لن تجتاز مقابلة للعمل كمصمم في أي شركة إلكترونية دقيقة. في النهاية ، المسار من FPGA إلى ASIC ، ودارات الكتلة الموجودة في أجهزة تسريع أجهزة iPhones و Tesla و AI.يحتوي الكتاب على مقابلة مع فريق من سانت بطرسبرغ جلبته شركة إنتل إلى مقرها الرئيسي في وادي السليكون لفوزهم في مسابقة Innovate FPGA. كتاب "التوليف الرقمي: دورة عملية"Cadence Design Systems ، شركة رائدة في أتمتة تصميم الدوائر المصغرة ، مدعومة (في الصورة أعلاه ، تقف سيبيريا ناتاشا مع لوحة FPGA أمام المقر الرئيسي لـ Cadence في وادي السيليكون - سيكون الفيديو الخاص بها في البريد).تم إنشاء Labnik تحت رعاية المدرسة العليا للاقتصاد / MIEM (ألكسندر رومانوف ، فيرونيكا بروخوروفا وإيجور أغاميرزيان) ، بينما كتب فصول مختلفة من قبل معلمين من جامعات موسكو وكييف وسمارة ، وسانت بطرسبرغ ITMO ، و Chernihiv Polytechnic ، وجامعة كاليفورنيا سانتا كروز ( تشارلز دانشيك ، مكتب مسائي في وادي السيليكون). حضر إنشاء الكتاب المدرسي مهندسون من شركة IVA Technologies الروسية (ستانيسلاف زيلنيو ، مسرع الأجهزة AI + مدرسة المشروع التعليمي MIPS) و FSUE NPTSAP(قسم Roscosmos) والشركات الأمريكية MIPS و Juniper Networks و AMD. نشر كتاب DMK-Press.لقد وضعت خطة للمختبر وجذبت المؤلفين من المشاريع التعليمية السابقة ، وبعد ذلك نقلت السيطرة إلى ألكسندر رومانوف ، الذي قام بعمل شاق ، وأدار المشروع لمدة عامين تقريبًا. يتناسب إنشاء الكتاب المدرسي بشكل طبيعي مع أنشطة ألكسندر ، الذي رفع المختبر في HSE MIEM لمدة 3 سنوات ، والذي يتعامل مع أجهزة الكمبيوتر المدمجة والروبوتات و FPGA. نظم المختبر عدة فرق في Innovate FPGA ، وأصبح أحدها حاصل على ميدالية برونزية في النهائيات الإقليمية.الكتاب الدراسي ليس مناسبًا للطلاب فقط - يمكن استخدامه في المعسكرات الصيفية للتصميم الرقمي للطلاب المتقدمين. إن فهم البرامج التعليمية على الإنترنت من البداية حول كيفية العمل مع بيئة Intel Quartus II ليس أمرًا تافهًا. وفي الكتاب الدراسي يتم وصف كل شيء في الخطوات. بالإضافة إلى ذلك ، فإنه يحتوي على كل الأسس النظرية للقيام بشيء مثير للاهتمام لأطفال المدارس ، بالإضافة إلى الأضواء الوامضة التي تزعجهم بسرعة. من المثير للاهتمام على سبيل المثال لعبة فيديو: إن فكرة التعلم فيريلو عبر ألعاب VGA ليست جديدة - فالكثير من الجامعات لديها مثل هذا المختبر ، على سبيل المثال ، في معهد ماساتشوستس للتكنولوجيا (MIT) 6.111 مختبر الأنظمة الرقمية التمهيدية. أيضًا ، قبل عامين ، تم نشر كتاب Designing Video Game Hardware in Verilog Paperback بواسطة Steven Hugg ، مع ألعاب تم تطويرها إلى حد ما مع الدبابات وسيارات السباق ومولد السماء المرصعة بالنجوم العشوائية باستخدام LFSR ومخزن الإطارات المؤقت وحتى واجهة برامج الأجهزة. بالإضافة إلى ذلك ، توجد ألعاب VGA في عروض تجريبية من الشركات المصنعة لـ FPGAs Xilinx و Intel / Altera ، وبشكل أدق من الشركات الشريكة - Digilent و Terasic.

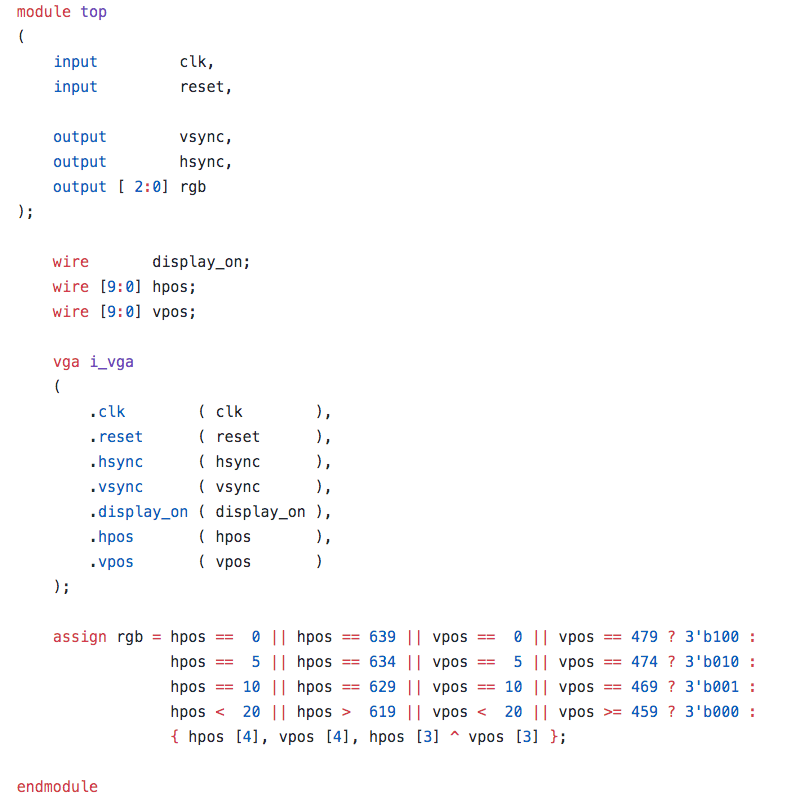

إن فكرة التعلم فيريلو عبر ألعاب VGA ليست جديدة - فالكثير من الجامعات لديها مثل هذا المختبر ، على سبيل المثال ، في معهد ماساتشوستس للتكنولوجيا (MIT) 6.111 مختبر الأنظمة الرقمية التمهيدية. أيضًا ، قبل عامين ، تم نشر كتاب Designing Video Game Hardware in Verilog Paperback بواسطة Steven Hugg ، مع ألعاب تم تطويرها إلى حد ما مع الدبابات وسيارات السباق ومولد السماء المرصعة بالنجوم العشوائية باستخدام LFSR ومخزن الإطارات المؤقت وحتى واجهة برامج الأجهزة. بالإضافة إلى ذلك ، توجد ألعاب VGA في عروض تجريبية من الشركات المصنعة لـ FPGAs Xilinx و Intel / Altera ، وبشكل أدق من الشركات الشريكة - Digilent و Terasic. على وجه الخصوص ، في المختبر من معهد ماساتشوستس للتكنولوجيامن الواضح تمامًا أن كل ما عليك القيام به لرسم على الشاشة هو تنفيذ وظيفة في شكل رسم بياني يأخذ الإحداثيات X و Y لنقطة على الشاشة كوسيطة ويعيد لون تلك النقطة (RGB). في أبسط الحالات ، هذه الوظيفة هي وظيفة تركيبة ، على سبيل المثال ، ستقوم هذه الوظيفة برسم تحفة ماليفيتش: "اللون أسود (RGB = 0،0،0) إذا كان x> = 200 و x <= 400 و y> = 200 و y <400 ، وإلا أبيض (RGB = 1،1،1). " سوف نطلق على هذه الدائرة اسم "الخلاط" ، لأنها "ستمزج" المدخلات من مولدات الصور المختلفة.لتوليد وسيطات الخلاط X و Y بأنفسهم ، يتم استخدام دارة بسيطة ذات عددين تستخدم إشارة ساعة CLK. بالإضافة إلى إحداثيات X و Y ، تولد هذه الدائرة أيضًا إشارات HSYNC و VSYNC لعرض VGA. ظلت إشارات HSYNC و VSYNC منذ وقت أنبوب أشعة الكاثود. يخبرون الشعاع الظاهري بوقت الانتقال إلى النقطة / البكسل التالي على الشاشة أفقيًا ، ثم إلى الصف التالي عموديًا.في الحالة الصعبة ، لا يستخدم الخلاط قيم المدخلات X و Y فحسب ، بل يستخدم أيضًا القيم من عناصر الحالة (D-flip-flops and memory) ، والتي يتم تسجيلها باستخدام إشارة ساعة CLK. في هذه الحالة ، تدخل الساعة أيضًا إلى الخلاط. تسمى الدوائر ذات إشارات الساعة وعناصر الحالة بالتسلسل (تمر هذه الدوائر عبر سلسلة من الحالات التي تنبض بوضوح إشارة ساعة نبضية). في الخلاطات المتتابعة ، يمكنك تنفيذ صور متحركة لأي درجة من التعقيد.هذه هي الصور من مختبر MIT shnaya (نفس الصورة في كومة جامعات أخرى) توضح وظيفة مولد HSYNC / VSYNC ، الخلاط (من نفس الوحدة التي تحسب RGB كوظيفة X / HCOUNT و Y / VCOUNT) ، بالإضافة إلى إخراج HSYNC ، VSYNC و RGB على الشاشة. تستخدم الصورة مفتاح / معدد إرسال بين ثلاث خلاطات - واحد يرسم خطوطًا ، والآخر يرسم مستطيلًا ، والثالث يرسم صورة على الشاشة أثناء لعب كرة الطاولة:

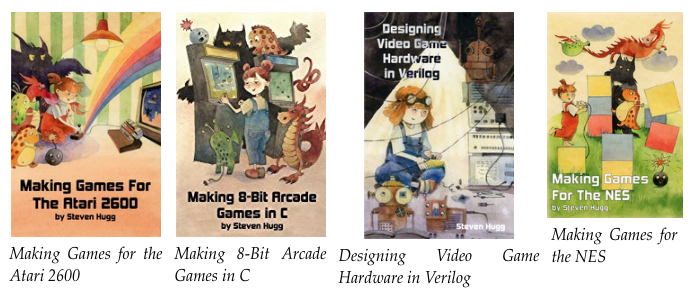

على وجه الخصوص ، في المختبر من معهد ماساتشوستس للتكنولوجيامن الواضح تمامًا أن كل ما عليك القيام به لرسم على الشاشة هو تنفيذ وظيفة في شكل رسم بياني يأخذ الإحداثيات X و Y لنقطة على الشاشة كوسيطة ويعيد لون تلك النقطة (RGB). في أبسط الحالات ، هذه الوظيفة هي وظيفة تركيبة ، على سبيل المثال ، ستقوم هذه الوظيفة برسم تحفة ماليفيتش: "اللون أسود (RGB = 0،0،0) إذا كان x> = 200 و x <= 400 و y> = 200 و y <400 ، وإلا أبيض (RGB = 1،1،1). " سوف نطلق على هذه الدائرة اسم "الخلاط" ، لأنها "ستمزج" المدخلات من مولدات الصور المختلفة.لتوليد وسيطات الخلاط X و Y بأنفسهم ، يتم استخدام دارة بسيطة ذات عددين تستخدم إشارة ساعة CLK. بالإضافة إلى إحداثيات X و Y ، تولد هذه الدائرة أيضًا إشارات HSYNC و VSYNC لعرض VGA. ظلت إشارات HSYNC و VSYNC منذ وقت أنبوب أشعة الكاثود. يخبرون الشعاع الظاهري بوقت الانتقال إلى النقطة / البكسل التالي على الشاشة أفقيًا ، ثم إلى الصف التالي عموديًا.في الحالة الصعبة ، لا يستخدم الخلاط قيم المدخلات X و Y فحسب ، بل يستخدم أيضًا القيم من عناصر الحالة (D-flip-flops and memory) ، والتي يتم تسجيلها باستخدام إشارة ساعة CLK. في هذه الحالة ، تدخل الساعة أيضًا إلى الخلاط. تسمى الدوائر ذات إشارات الساعة وعناصر الحالة بالتسلسل (تمر هذه الدوائر عبر سلسلة من الحالات التي تنبض بوضوح إشارة ساعة نبضية). في الخلاطات المتتابعة ، يمكنك تنفيذ صور متحركة لأي درجة من التعقيد.هذه هي الصور من مختبر MIT shnaya (نفس الصورة في كومة جامعات أخرى) توضح وظيفة مولد HSYNC / VSYNC ، الخلاط (من نفس الوحدة التي تحسب RGB كوظيفة X / HCOUNT و Y / VCOUNT) ، بالإضافة إلى إخراج HSYNC ، VSYNC و RGB على الشاشة. تستخدم الصورة مفتاح / معدد إرسال بين ثلاث خلاطات - واحد يرسم خطوطًا ، والآخر يرسم مستطيلًا ، والثالث يرسم صورة على الشاشة أثناء لعب كرة الطاولة: في الكود ، يبدو أبسط خلاط مثل هذا. يرسم مربعات متعددة الألوان من مزيج من الأحمر والأزرق والأخضر ، بالإضافة إلى خطوط من الألوان النقية:

في الكود ، يبدو أبسط خلاط مثل هذا. يرسم مربعات متعددة الألوان من مزيج من الأحمر والأزرق والأخضر ، بالإضافة إلى خطوط من الألوان النقية: بهذه الطريقة ، يمكنك رسم مجموعة متنوعة من الصور الثابتة الملونة. فيما يلي الصور التي رسمها الطلاب في مدرسة صيفية في زيلينوجراد مباشرة بعد محاضرة قصيرة تشرح كيفية القيام بذلك:

بهذه الطريقة ، يمكنك رسم مجموعة متنوعة من الصور الثابتة الملونة. فيما يلي الصور التي رسمها الطلاب في مدرسة صيفية في زيلينوجراد مباشرة بعد محاضرة قصيرة تشرح كيفية القيام بذلك: حسنًا ، يمكن لأطفال المدارس ترميز وظيفة RGB (X ، Y) ورسم صور ثابتة. ولكن ماذا تفعل بعد ذلك ، ما هي الخطوة التالية؟ درسنا إمكانية استخدام مواد من MIT و Digilent + Xilinx و Altera + Terasic و Steven Hugg ، وبعد ذلك توصلنا إلى استنتاج أنه لا يمكن استخدامها في شكلها النقي. يتم تضمين مختبرات الجامعة في برنامج الجامعة ، كما أن المواد من موردي FPGA ليست مكتوبة بشكل جيد ، ولا تحتوي أيضًا على نصائح حول كيفية تغيير الرمز في شكل مدرسة صيفية بحيث يخترع الطلاب ألعابهم. يحتوي كتاب ستيفن هوج على سلبيين هما الوجه الآخر لفضائله (الحيوية والحيوية):بشكل عام ، يقف verilog في Stephen Hugg على قدم المساواة مع برمجة معالجات وحدات التحكم القديمة 8 بت من Atari و Nintendo. وبالتالي ، لا يركز Hugg على تدريب المصممين الفائقين المستقبليين ، ولكن على الحنين إلى الماضي ، وعلماء الكمبيوتر الرجعيين وغيرهم من المُعيدين. الفرق بين بيئته وأدوات التصميم الاحترافية أكبر من ذلك بين بيئة برمجة Arduino ومجموعات الأدوات لـ STM32.

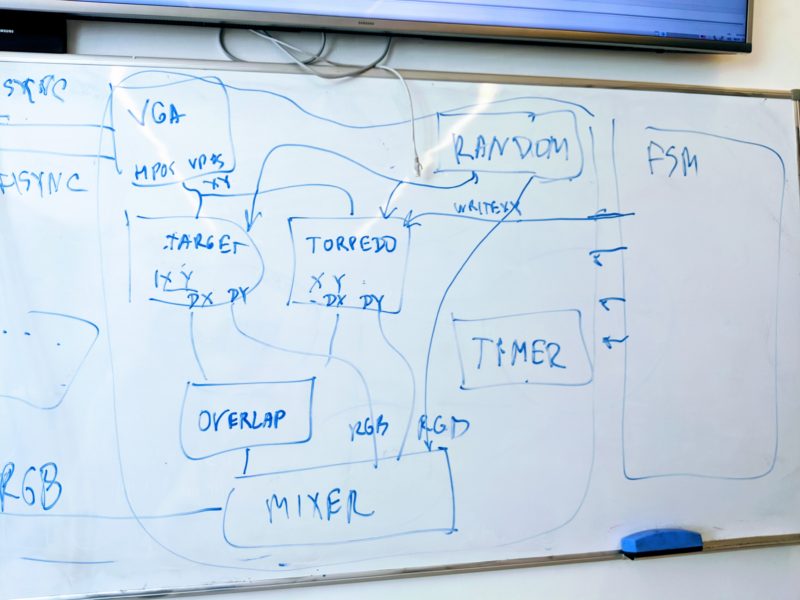

حسنًا ، يمكن لأطفال المدارس ترميز وظيفة RGB (X ، Y) ورسم صور ثابتة. ولكن ماذا تفعل بعد ذلك ، ما هي الخطوة التالية؟ درسنا إمكانية استخدام مواد من MIT و Digilent + Xilinx و Altera + Terasic و Steven Hugg ، وبعد ذلك توصلنا إلى استنتاج أنه لا يمكن استخدامها في شكلها النقي. يتم تضمين مختبرات الجامعة في برنامج الجامعة ، كما أن المواد من موردي FPGA ليست مكتوبة بشكل جيد ، ولا تحتوي أيضًا على نصائح حول كيفية تغيير الرمز في شكل مدرسة صيفية بحيث يخترع الطلاب ألعابهم. يحتوي كتاب ستيفن هوج على سلبيين هما الوجه الآخر لفضائله (الحيوية والحيوية):بشكل عام ، يقف verilog في Stephen Hugg على قدم المساواة مع برمجة معالجات وحدات التحكم القديمة 8 بت من Atari و Nintendo. وبالتالي ، لا يركز Hugg على تدريب المصممين الفائقين المستقبليين ، ولكن على الحنين إلى الماضي ، وعلماء الكمبيوتر الرجعيين وغيرهم من المُعيدين. الفرق بين بيئته وأدوات التصميم الاحترافية أكبر من ذلك بين بيئة برمجة Arduino ومجموعات الأدوات لـ STM32. بالطبع ، لا أقترح إلقاء اللوم على Cadence SimVision و Synopsys Design Compiler لأطفال المدارس بمئات الآلاف من الدولارات ، ولكن قد يحصل أطفال المدارس على إصدارات مجانية من الأدوات الاحترافية Xilinx Vivado و Intel / Altera Quartus II و Mentor ModelSim ، بالإضافة إلى Icarus Verilog و GTKWave و edaplayground عبر الإنترنت . كوم .لقد أعدت قراءة الفقرة السابقة وفكرت: ولكن كان من الممكن استخدام Cadence SimVision للمدرسة الصيفية في Zelenograd. لقد أصبحت أفضل وأكثر ملاءمة لها ومنافسها المباشر بيئة رؤية تصميم Synopsys (DVE) * ، والأموال من Mentor Graphics (طراز ModelSim مجاني و Questa مدفوع الأجر) ، وجميع الأدوات الرخيصة والمجانية (IcarusVerilog ، وما إلى ذلك) إذا كان فرع Cadence في موسكو سيعطينا نظام التصميم الحق والدعم لاستخدام برامجهم في المدارس الصيفية في Zelenograd ، وأنا شخصيًا سأقوم بدمج هذا في المناهج الدراسية.* بالنسبة لـ DVE ، على سبيل المثال ، فإن النص الموجود في نافذة المصدر هو عربات التي تجرها الدواب / القفز عندما أقوم بتشغيله تحت Ubuntu. لا بد لي من القيام بتغيير حجم النافذة حتى يتوقف عن الفشل. ليس لدى SimVision هذا.في ما يلي بداية البرنامج التعليمي لـ SimVision (إجمالي 22 مقطع فيديو):لكن عد إلى الألعاب. إن لم يكن ستيفن هوج ، فماذا بعد؟ كتبت مثالاً على لعبة بسيطة استخدمتها في مدرسة صيفية في زيلينوجراد . مصادر اللعبة على جيثب . تبدو هكذا:لمدة أسبوعين ، اكتشف الطلاب المبادئ الأساسية للتصميم على مستوى نقل التسجيلات وبدأوا في صنع ألعابهم الخاصة وغير العادية:لنتحدث عن التفاصيل الفنية للعبة مثال. يمكن وضع وحدة ألعاب مستقلة عن المنصة (فورية) في غلاف أي لوحة FPGA تحتوي على منفذ VGA وزرين. إذا كانت اللوحة عارية تمامًا ، فيمكنك توصيل محول لـ VGA والأزرار من خلال أسلاك GPIO (إدخال / إخراج للأغراض العامة). تتكون وحدة اللعبة من:

بالطبع ، لا أقترح إلقاء اللوم على Cadence SimVision و Synopsys Design Compiler لأطفال المدارس بمئات الآلاف من الدولارات ، ولكن قد يحصل أطفال المدارس على إصدارات مجانية من الأدوات الاحترافية Xilinx Vivado و Intel / Altera Quartus II و Mentor ModelSim ، بالإضافة إلى Icarus Verilog و GTKWave و edaplayground عبر الإنترنت . كوم .لقد أعدت قراءة الفقرة السابقة وفكرت: ولكن كان من الممكن استخدام Cadence SimVision للمدرسة الصيفية في Zelenograd. لقد أصبحت أفضل وأكثر ملاءمة لها ومنافسها المباشر بيئة رؤية تصميم Synopsys (DVE) * ، والأموال من Mentor Graphics (طراز ModelSim مجاني و Questa مدفوع الأجر) ، وجميع الأدوات الرخيصة والمجانية (IcarusVerilog ، وما إلى ذلك) إذا كان فرع Cadence في موسكو سيعطينا نظام التصميم الحق والدعم لاستخدام برامجهم في المدارس الصيفية في Zelenograd ، وأنا شخصيًا سأقوم بدمج هذا في المناهج الدراسية.* بالنسبة لـ DVE ، على سبيل المثال ، فإن النص الموجود في نافذة المصدر هو عربات التي تجرها الدواب / القفز عندما أقوم بتشغيله تحت Ubuntu. لا بد لي من القيام بتغيير حجم النافذة حتى يتوقف عن الفشل. ليس لدى SimVision هذا.في ما يلي بداية البرنامج التعليمي لـ SimVision (إجمالي 22 مقطع فيديو):لكن عد إلى الألعاب. إن لم يكن ستيفن هوج ، فماذا بعد؟ كتبت مثالاً على لعبة بسيطة استخدمتها في مدرسة صيفية في زيلينوجراد . مصادر اللعبة على جيثب . تبدو هكذا:لمدة أسبوعين ، اكتشف الطلاب المبادئ الأساسية للتصميم على مستوى نقل التسجيلات وبدأوا في صنع ألعابهم الخاصة وغير العادية:لنتحدث عن التفاصيل الفنية للعبة مثال. يمكن وضع وحدة ألعاب مستقلة عن المنصة (فورية) في غلاف أي لوحة FPGA تحتوي على منفذ VGA وزرين. إذا كانت اللوحة عارية تمامًا ، فيمكنك توصيل محول لـ VGA والأزرار من خلال أسلاك GPIO (إدخال / إخراج للأغراض العامة). تتكون وحدة اللعبة من:- مولد مسح VGA.

- وحدتان عمل متوازيتان لطوربيدات العفريت وأهداف العفريت.

- آلة الدولة لسيناريو اللعبة ، مع الولايات "ابدأ" ، "التوجيه" ، "الذباب" ، "النصر / الهزيمة".

- وحدة نمطية تحدد ما إذا كانت التصادمات تصادمت.

- جهاز ضبط الوقت لتعيين مدة التأثير المرئي بعد الفوز (وميض شاشة التوت) أو الهزيمة (الشاشة الصفراء).

بالنسبة للمدرسة التالية ، يجب إعادة رسم جميع هذه الصور باستخدام draw.io أو Lucidchart في المخططات العادية للهندسة المعمارية الدقيقة:

بالنسبة للمدرسة التالية ، يجب إعادة رسم جميع هذه الصور باستخدام draw.io أو Lucidchart في المخططات العادية للهندسة المعمارية الدقيقة: تحتاج أيضًا إلى إضافة مخططات زمنية مرسومة باستخدام WaveDrom إلى مواد المدرسة لإظهار كيفية عمل مولد مسح VGA وكيف يحسب خط الأنابيب المصغر الإحداثيات مسار البيانات داخل العفاريت:

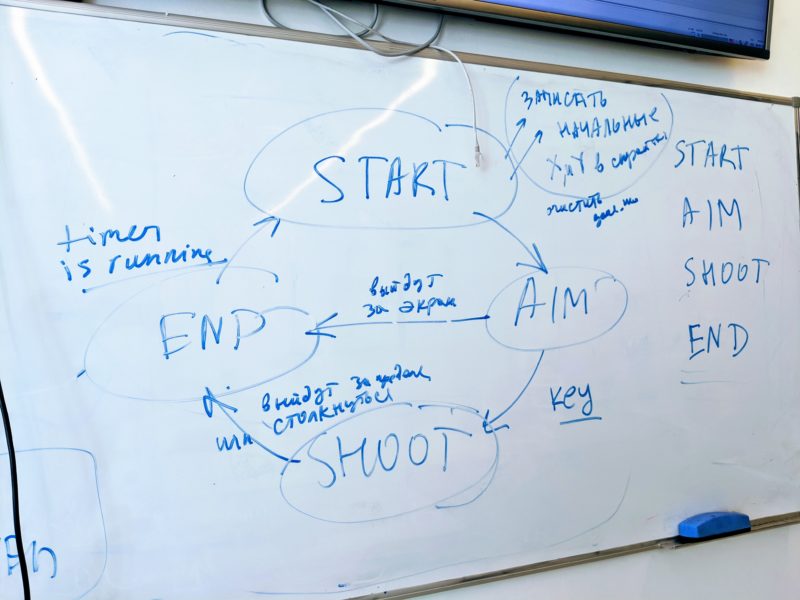

تحتاج أيضًا إلى إضافة مخططات زمنية مرسومة باستخدام WaveDrom إلى مواد المدرسة لإظهار كيفية عمل مولد مسح VGA وكيف يحسب خط الأنابيب المصغر الإحداثيات مسار البيانات داخل العفاريت: وبالطبع تحتاج إلى رسم مخططات لجهاز الحالة المحدودة. لقد صنعت عشرات المتغيرات من آلة الحالة المحدودة لهذه اللعبة ، هنا على اللوحة هناك متغير مع أربع ولايات:

وبالطبع تحتاج إلى رسم مخططات لجهاز الحالة المحدودة. لقد صنعت عشرات المتغيرات من آلة الحالة المحدودة لهذه اللعبة ، هنا على اللوحة هناك متغير مع أربع ولايات: لماذا قمت بالعديد من الخيارات؟ حتى مع مثل هذه الآلة البسيطة ، يمكنك مقارنة الأنماط المختلفة لترميزها في ملف ، وكذلك توضيح تحسين الحالات والتوقيت. كل هذا مطلوب في مقابلة لمنصب كمصمم شرائح في Apple و NVidia و Intel و AMD وغيرها من الشركات. لذلك ، يجب أن تعرف هذه المنطقة بحيث ترتد الأسنان. هناك بعض مقالات كليفورد كامينغز الجيدة حول هذا الموضوع:

لماذا قمت بالعديد من الخيارات؟ حتى مع مثل هذه الآلة البسيطة ، يمكنك مقارنة الأنماط المختلفة لترميزها في ملف ، وكذلك توضيح تحسين الحالات والتوقيت. كل هذا مطلوب في مقابلة لمنصب كمصمم شرائح في Apple و NVidia و Intel و AMD وغيرها من الشركات. لذلك ، يجب أن تعرف هذه المنطقة بحيث ترتد الأسنان. هناك بعض مقالات كليفورد كامينغز الجيدة حول هذا الموضوع:- أحدث مقال لعام 2019: تصميم وتركيب FiniteStateMachine (FSM) باستخدام SystemVerilog - Part I بواسطة Clifford E.Cummings & Heath Chambers.

- , one-hot state machine, SPARC MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. . 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- , 9 , : Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

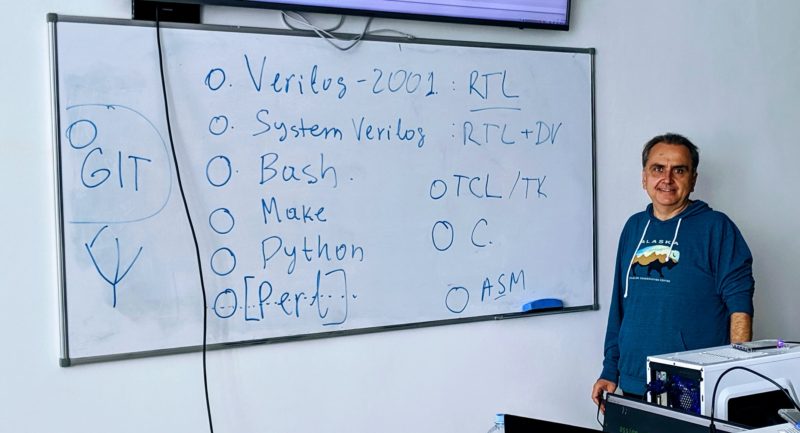

لقد جمعت إصدارات مختلفة من جهاز حالة اللعبة باستخدام أداة Synopsys Design Compiler الأكثر شيوعًا في الصناعة وصنعت مثل هذا الجهاز اللوحي. كما نرى ، فإن الإصدار الحديث من DC يحسن جميع الأنماط بكفاءة عالية ، لذا فإن سحب البيكو ثانية على أجهزة الحالة ممكن ، ولكنه ليس ضروريًا. على الرغم من إمكانية استخدام آلات الحالة المحدودة الأكثر تعقيدًا ، إلا أن الحيل من مقالات Cummings ستكون أكثر أهمية: خلال المدرسة في Zelenograd ، ناقشنا أيضًا أنه في تصميم الرقائق ، بالإضافة إلى لغات الوصف لمعدات Verilog و VHDL ، يتم استخدام العديد من اللغات المساعدة:

خلال المدرسة في Zelenograd ، ناقشنا أيضًا أنه في تصميم الرقائق ، بالإضافة إلى لغات الوصف لمعدات Verilog و VHDL ، يتم استخدام العديد من اللغات المساعدة:يتم استخدام Python لأتمتة التجميع ، وإدارة الانحدار ، واستخراج المعلومات من تقارير التوليف وإنشاء التعليمات البرمجية ، بالإضافة إلى bash ، make ، وغيرها من مطابخ Unix / Linux.

Tcl/Tk , . , , Verilog FPGA, , .

1990- Perl . Perl . Verilog-2001 SystemVerilog 90% Verilog-2001 generate SystemVerilog, , . , , SystemVerilog.

يتم استخدام C / C ++ والمكتبات مثل SystemC لكتابة نماذج كتلة الأجهزة على مستوى المعاملة. يقوم مهندسو التحقق بفحص الكتل المصممة على الشريان مقابل هذه النماذج.

إذا كنت تعمل في شركة معالج ، فمن الجيد بالنسبة لك أن تعرف المجمع. حتى إذا لم تكن مبرمجًا منخفض المستوى ولست متحققًا ، لكنك مصمم معالج على مستوى عمليات نقل التسجيل (Register Transfer Level - RTL).

فيما يلي روابط للراغبين في استخدام اللؤلؤ كمعالج أولي لل Verilogue:- ج. سبيفي. EP3: معالج بيرل الموسعة

- vpp.pl صفحة رجل

- معالج فيريلوج

مثال على كيفية استخدام لؤلؤة verlog المضمنة لتوصيل 64 منفذًا://@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

سيكون من الجيد إذا كتب شخص ما نصوصًا عالمية لنمذجة وتجميع مثال (ليس بالضرورة لعبتي) على جميع المنصات الرئيسية للتوليف ، والمحاكاة ، وتصحيح الأخطاء ، وتحليل استهلاك الطاقة الديناميكي ، والتصميم المادي ، والتجليد لجميع اللوحات ، وما إلى ذلك. يمكن استخدام ذلك في المدارس والندوات:

سيكون من الجيد إذا كتب شخص ما نصوصًا عالمية لنمذجة وتجميع مثال (ليس بالضرورة لعبتي) على جميع المنصات الرئيسية للتوليف ، والمحاكاة ، وتصحيح الأخطاء ، وتحليل استهلاك الطاقة الديناميكي ، والتصميم المادي ، والتجليد لجميع اللوحات ، وما إلى ذلك. يمكن استخدام ذلك في المدارس والندوات: هنا قد يكون لديك سؤال: لماذا أستخدم ندوات لينكس؟ على الرغم من أن Windows يحتوي أيضًا على بيئة النمذجة والتوليف لـ FPGAs ، إلا أن Windows لم يتجذر في صناعة تصميم الرقائق الشامل. في أوائل التسعينات ، تم تقسيم سوق محطات العمل لمطوري ASIC بين SunOS و HP / UX. ثم لعبت الشركات الإلكترونية لمدة ثلاث سنوات مع Windows NT ، لكنها لم تنجح. بعد ذلك ، بصق Synopsys وشركات برامج التصميم الأخرى وتحولت إلى Linux - أولاً على Red Hat ، ثم على SuSE و Ubuntu. أظن ، بشكل رئيسي بسبب مجموعة من البرامج النصية على اللؤلؤ ، C-shell ، وما إلى ذلك ، وكذلك بسبب العمل عن بعد للمطورين من خلال telnet و X Window.لذلك ، بالنسبة لندواتي ، أذهب مع مجموعة من أقراص SSD القابلة للتشغيل مع Lubuntu ، حيث يتم تثبيت جميع البرامج الضرورية. أستخدم التمهيد القديم ، ولكن تبين مؤخرًا أن المزيد والمزيد من أجهزة الكمبيوتر تتطلب تمهيد UEFI. على ما يبدو ، ستحتاج إلى إنشاء قرص SSD قابل للتشغيل مع تمهيد UEFI.تستخدم الشركات سريعة الحركة CentOS بدلاً من Red Hat. ربما تدخل العديد من أدوات التصميم تحت Debian ، لكنني لم أختبرها.

هنا قد يكون لديك سؤال: لماذا أستخدم ندوات لينكس؟ على الرغم من أن Windows يحتوي أيضًا على بيئة النمذجة والتوليف لـ FPGAs ، إلا أن Windows لم يتجذر في صناعة تصميم الرقائق الشامل. في أوائل التسعينات ، تم تقسيم سوق محطات العمل لمطوري ASIC بين SunOS و HP / UX. ثم لعبت الشركات الإلكترونية لمدة ثلاث سنوات مع Windows NT ، لكنها لم تنجح. بعد ذلك ، بصق Synopsys وشركات برامج التصميم الأخرى وتحولت إلى Linux - أولاً على Red Hat ، ثم على SuSE و Ubuntu. أظن ، بشكل رئيسي بسبب مجموعة من البرامج النصية على اللؤلؤ ، C-shell ، وما إلى ذلك ، وكذلك بسبب العمل عن بعد للمطورين من خلال telnet و X Window.لذلك ، بالنسبة لندواتي ، أذهب مع مجموعة من أقراص SSD القابلة للتشغيل مع Lubuntu ، حيث يتم تثبيت جميع البرامج الضرورية. أستخدم التمهيد القديم ، ولكن تبين مؤخرًا أن المزيد والمزيد من أجهزة الكمبيوتر تتطلب تمهيد UEFI. على ما يبدو ، ستحتاج إلى إنشاء قرص SSD قابل للتشغيل مع تمهيد UEFI.تستخدم الشركات سريعة الحركة CentOS بدلاً من Red Hat. ربما تدخل العديد من أدوات التصميم تحت Debian ، لكنني لم أختبرها. بالنسبة للندوات ، أستخدم لوحات FPGA الصينية ، واحدة منها في أيدي يدي فتاة نوفوسيبيرسك ، ناتاشا ، التي تستضيف حفلات What-Where-When في وادي السيليكون .

بالنسبة للندوات ، أستخدم لوحات FPGA الصينية ، واحدة منها في أيدي يدي فتاة نوفوسيبيرسك ، ناتاشا ، التي تستضيف حفلات What-Where-When في وادي السيليكون . في شهر مارس ، مشيت عبر الحياة البرية في كاليفورنيا مع رجل الأعمال الروسي سيرجي زورين، التي نقلت عشرات من لوحات ZEOWAA إلى موسكو ، مماثلة في الخصائص التي تحملها ناتاشا في أيديهم.نظرًا لأنه ربما لن تكون هناك ندوات في Zelenograd بسبب الفيروس التاجي هذا الصيف ، أعتقد أنني سأمنح هذه العشرات من الرسوم لأطفال المدارس في موسكو مجانًا (UPD: يمكن لأطفال المدارس من مدن أخرى أيضًا ، على الرغم من وجود ضجة إضافية مع إعادة التوجيه). بشرطين:

في شهر مارس ، مشيت عبر الحياة البرية في كاليفورنيا مع رجل الأعمال الروسي سيرجي زورين، التي نقلت عشرات من لوحات ZEOWAA إلى موسكو ، مماثلة في الخصائص التي تحملها ناتاشا في أيديهم.نظرًا لأنه ربما لن تكون هناك ندوات في Zelenograd بسبب الفيروس التاجي هذا الصيف ، أعتقد أنني سأمنح هذه العشرات من الرسوم لأطفال المدارس في موسكو مجانًا (UPD: يمكن لأطفال المدارس من مدن أخرى أيضًا ، على الرغم من وجود ضجة إضافية مع إعادة التوجيه). بشرطين:قبل أن تحصل على لوحة ، تحتاج إلى مراجعة الأجزاء الثلاثة للدورة عبر الإنترنت "كيف يعمل مبدعو رقائق النانو الذكية" ( "من الترانزستور إلى الدائرة المصغرة" ، "الجانب المنطقي للدوائر الرقمية" ، "الجانب المادي للدوائر الرقمية" ) ، والحصول على شهادة. أنشأنا هذه الدورة مع RUSNANO ، أو بالأحرى ابنته التعليمية eNano ، مشروع STEMford.

, , , . , , , ( ) . , , .

, , .

إذا كنت ترغب في شراء كتاب جديد "التوليف المنطقي" كمساعدة لمثل هذا المشروع ، فعندئذٍ لدى قرائها هبر لديها رمز ترويجي - Sintez_2020. في المستقبل ، سيكون من الجيد النزول باستخدام الألواح الصينية وإنشاء لوحة روسية رخيصة لمثل هذه التمارين مع FPGA ، مع تصميم مفتوح. أرحب إذا كنت تشارك أفكارك في التعليقات على برنامج تصميم اللوحة والأفكار حول كيفية تصميم وتسويق مثل هذا المنتدى بشكل أفضل. للاستخدام الجماعي مع أطفال المدارس ، من المستحسن ألا يكلف أكثر من 30 دولارًا أو 2000 روبل.

في المستقبل ، سيكون من الجيد النزول باستخدام الألواح الصينية وإنشاء لوحة روسية رخيصة لمثل هذه التمارين مع FPGA ، مع تصميم مفتوح. أرحب إذا كنت تشارك أفكارك في التعليقات على برنامج تصميم اللوحة والأفكار حول كيفية تصميم وتسويق مثل هذا المنتدى بشكل أفضل. للاستخدام الجماعي مع أطفال المدارس ، من المستحسن ألا يكلف أكثر من 30 دولارًا أو 2000 روبل. إذا كنت طالبًا ومهتمًا بتصميم الدوائر المصغرة ، فيمكنك الانتقال إلى MIET و HSE MIEM ومعهد موسكو للهندسة الفيزيائية وجامعة موسكو الحكومية ومعهد موسكو للفيزياء والتكنولوجيا (تشارك نيكيتا بولياكوف في مثل هذه التمارين، MPEI ، MISiS ، ITMO ، LETI ، جامعة سمارة ، بعض الجامعات الأوكرانية (KNU ، Chernihiv NTU ، Kharkov KNURE) وجامعات أخرى. لذلك وجدت كيف يتم إصلاح توجهي إلى لجنة اختيار MIET في Zelenograd:

إذا كنت طالبًا ومهتمًا بتصميم الدوائر المصغرة ، فيمكنك الانتقال إلى MIET و HSE MIEM ومعهد موسكو للهندسة الفيزيائية وجامعة موسكو الحكومية ومعهد موسكو للفيزياء والتكنولوجيا (تشارك نيكيتا بولياكوف في مثل هذه التمارين، MPEI ، MISiS ، ITMO ، LETI ، جامعة سمارة ، بعض الجامعات الأوكرانية (KNU ، Chernihiv NTU ، Kharkov KNURE) وجامعات أخرى. لذلك وجدت كيف يتم إصلاح توجهي إلى لجنة اختيار MIET في Zelenograd: ولكن هنا كيف تبدو MIET في الداخل: يمكنك

ولكن هنا كيف تبدو MIET في الداخل: يمكنك العثور على وظيفة هناك مقابل MIET لمنظمة ELVIS غير الحكومية ، والتي تتعامل مع الكاميرات الذكية ورقائق الأقمار الصناعية:

العثور على وظيفة هناك مقابل MIET لمنظمة ELVIS غير الحكومية ، والتي تتعامل مع الكاميرات الذكية ورقائق الأقمار الصناعية: أو يمكنك القدوم إلى وادي السيليكون. تريد الحصول على مقابلة مع Dolina؟ تدرب على لوحات FPGA!

أو يمكنك القدوم إلى وادي السيليكون. تريد الحصول على مقابلة مع Dolina؟ تدرب على لوحات FPGA!